# A comparison between tightly coupled and loosely coupled processors in multicore systems

Maryam Kohansal

RPTU Kaiserslautern, Department of Computer Science

*Abstract - In the era of advanced computing, multicore processors have become essential for meeting the demands of high-performance applications, from smartphones to autonomous vehicles. These processors, which integrate multiple processing cores on a single chip, enable parallel execution of tasks, significantly enhancing speed, efficiency, and responsiveness. However, multicore architectures vary widely, with two primary designs dominating the field: tightly coupled and loosely coupled processors. Tightly coupled systems, characterized by shared memory and high-speed communication, excel in low-latency, compute-intensive tasks such as real-time robotic control, image processing, and scientific simulations. Loosely coupled systems, featuring distributed memories and message-passing networks, offer scalability and resilience, making them ideal for distributed applications, such as data analysis on large-scale datasets. This paper discusses their inherent differences, communication mechanisms, performance characteristics, advantages, disadvantages, and future trends. It also highlights how these architectures address the unique challenges of embedded systems and robotics, where performance, energy efficiency, and reliability are paramount. The findings underscore the importance of understanding these architectures for effective design and optimization, fostering informed decisions in system design.*

## 1 Introduction

The evolution of multicore processors began in the early 2000s, when the performance limits of single-core processors became apparent. Increasing clock speeds resulted in excessive power consumption and heat generation, making further scaling impractical. To overcome these challenges, processor manufacturers shifted toward parallelism, integrating multiple cores on a single chip. This shift has had a significant impact on embedded systems and robotics, where compact, efficient, and responsive processors are essential.

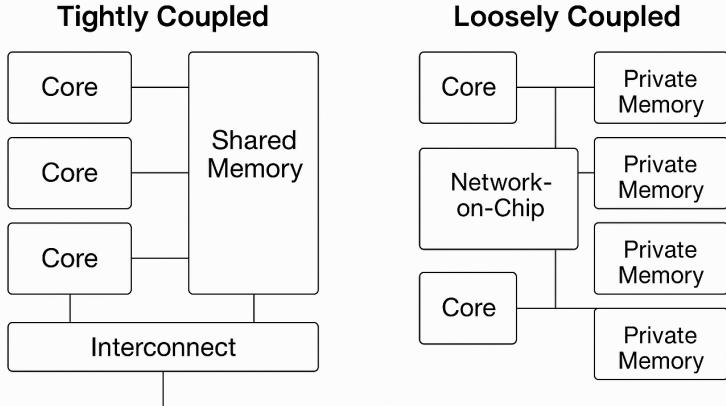

Within the landscape of multicore architectures, two primary approaches dominate: **tightly coupled** and **loosely coupled** processors. Tightly coupled systems feature cores that share a common memory pool and communicate via high-speed on-chip interconnects such as buses, cross-bar switches, or ring topologies [1]. This design enables rapid data exchange and synchronization, making it well suited for applications requiring low-latency communication, such as real-time

robotic control or embedded vision systems.

Loosely coupled systems, on the other hand, provide each core with its own private memory and rely on message-passing mechanisms such as Networks-on-Chip (NoC) or Ethernet [1]. While this architecture introduces higher communication latency, it improves scalability and fault tolerance, making it ideal for distributed applications such as cloud analytics, IoT infrastructures, and large-scale sensor networks.

A representative workload for evaluating these architectures is **General Matrix Multiply (GEMM)**, a core linear algebra operation that underpins applications ranging from machine learning to scientific simulations [4]. In tightly coupled systems, GEMM benefits from shared memory, enabling low-latency access to data. In loosely coupled systems, the workload is partitioned among cores, with results exchanged through explicit communication. This highlights the fundamental trade-offs between the two designs, particularly in the context of embedded and robotic systems.

This seminar report provides a structured comparison of tightly and loosely coupled multicore processors, emphasizing their architecture, communication networks, performance, advantages and disadvantages, and relevance for embedded system design. The remainder of this report is organized as follows:

- Section 2 introduces definitions and background.

- Section 3 reviews related work.

- Section 4 presents a detailed technical comparison.

- Section 5 illustrates practical examples of both architectures.

- Section 6 discusses architectural considerations for embedded system design.

- Section 7 concludes the report and highlights key takeaways.

## 2 Definition and Background

A processor, or central processing unit (CPU), is the core component of a computer system responsible for executing instructions, performing computations, and coordinating data flow. Traditionally, processors contained only a single core, meaning tasks were executed sequentially. As computational demands grew, particularly in applications such as video processing, robotics, and scientific simulations, single-core processors became a bottleneck.

To address these limitations, **parallel processing architectures** were introduced. These architectures are broadly classified into two main categories:

- **Single Instruction, Multiple Data (SIMD):** A single instruction operates on multiple data elements simultaneously. This model is particularly efficient for tasks with repetitive operations over large datasets. For instance, in graphics rendering, a GPU can apply the same arithmetic instruction to thousands of pixels in parallel, similar to a stamping machine producing identical patterns on multiple sheets of metal.

- **Multiple Instruction, Multiple Data (MIMD):** Different cores execute different instructions on different data simultaneously. This allows greater flexibility in task distribution. For example, in a robotics system, one core may process camera input while another controls motion actuators, enabling concurrent execution of heterogeneous tasks.

Most modern multicore processors adopt the MIMD model. Within MIMD, two architectural subtypes dominate: **tightly coupled** and **loosely coupled** processors [1, 3, 5].

- **Tightly coupled systems** use a single shared memory accessible by all cores through high-speed on-chip interconnects such as buses, crossbars, or ring topologies. This design supports rapid, low-latency communication, which is critical for real-time applications like automotive radar systems or embedded vision in robotics.

- **Loosely coupled systems** assign each core its own private memory and rely on message-passing protocols, often implemented via Networks-on-Chip (NoC) or Ethernet connections. This model enhances scalability and fault tolerance, making it better suited for large-scale distributed applications such as IoT-enabled smart cities or industrial monitoring systems.

A central workload relevant to both architectures is **General Matrix Multiply (GEMM)**, an essential operation in linear algebra used in machine learning (e.g., neural network training) and scientific computing (e.g., simulations in physics or fluid dynamics). In tightly coupled systems, GEMM benefits from fast access to shared data, while in loosely coupled systems, it is divided among independent cores that exchange partial results through communication networks [4].

The shift from single-core to multicore designs was driven by the physical limitations of clock frequency scaling in the late 1990s, where higher speeds caused excessive power consumption and heat. Early dual-core processors from Intel and AMD in the mid-2000s marked the commercial adoption of multicore architectures. Today, such processors are ubiquitous, powering devices from smartphones to supercomputers. In embedded systems and robotics, they enable real-time responsiveness, efficient energy use, and parallel data processing, underscoring the importance of understanding tightly and loosely coupled designs.

### 3 Related Work

The study of multicore processor architectures has attracted significant attention in computer architecture research, particularly as demand for high-performance computing in embedded systems and robotics continues to grow. Existing literature provides a valuable foundation for comparing tightly coupled and loosely coupled processors, highlighting their structural differences, performance trade-offs, and application domains.

Adeleye and Jiddah (2017) provide a broad overview of parallel architectures, including SIMD, tightly coupled MIMD, and loosely coupled MIMD systems [1]. Their analysis explains how tightly coupled systems rely on shared memory with high-speed interconnects, whereas loosely coupled systems use distributed memories with message-passing networks such as Network-on-Chip (NoC). They conclude that tightly coupled processors are advantageous for latency-sensitive applications, while loosely coupled processors are more effective for scalable, distributed workloads such as cluster computing.

Bates et al. (2014) focus on tightly coupled systems, presenting the **Loki architecture** as a case study [2]. Their work demonstrates how shared memory and efficient interconnects, such as crossbar switches, allow rapid data exchange for compute-intensive tasks, including General Matrix Multiply (GEMM) and convolutional neural networks (CNNs). They also emphasize the strengths of tightly coupled systems in real-time embedded tasks, while acknowledging challenges such as cache coherence overhead and limited scalability.

Sui et al. (2024) examine loosely coupled processors through the **MACO architecture**, designed specifically for GEMM acceleration [4]. Their study highlights how distributed memory

and NoC-based communication improve scalability and fault tolerance, making loosely coupled systems effective in large-scale data processing, deep learning, and IoT applications. However, they also point out that communication latency is a key limitation compared to tightly coupled systems.

Several educational resources, such as GeeksforGeeks (2024) and TechDifferences (2024), provide practical comparisons between tightly and loosely coupled architectures [3, 5]. These sources note that tightly coupled processors typically simplify programming by supporting models like OpenMP, while loosely coupled processors require more complex frameworks such as MPI. They further emphasize trade-offs in power efficiency, cost, and fault tolerance, helping to contextualize architectural decisions from a systems engineering perspective.

Taken together, these works establish a clear basis for comparing tightly and loosely coupled multicore processors. They show that tightly coupled designs excel in applications requiring low latency and synchronization, while loosely coupled designs prioritize scalability and modularity. However, most studies analyze each architecture in isolation or within specific domains. This report aims to fill that gap by providing a **structured, side-by-side comparison** that addresses architecture, communication models, performance, programming complexity, and suitability for embedded systems and robotics.

## 4 Technical Comparison

The structure of a multicore processor defines how cores are organized, how memory is managed, and how data flows between components. The architectural differences between tightly coupled and loosely coupled systems are fundamental to their performance and application domains, particularly in embedded systems and robotics where efficiency and responsiveness are critical.

### 4.1 Structure and Architecture

The structure of a multicore processor determines how its cores are arranged, how memory is managed, and how data moves between components. These architectural decisions directly influence the processor's performance, scalability, and suitability for specific applications.

#### 4.1.1 Tightly Coupled Processors

In tightly coupled systems, multiple processing cores are integrated onto a single chip and share a common main memory, which they access through high-speed on-chip interconnects such as buses, crossbar switches, or ring topologies [1]. This setup creates a unified memory space accessible to all cores—similar to a group of team members working on the same shared document [2].

A memory controller manages access to shared memory, ensuring synchronized operations. To improve performance and reduce memory latency, each core typically includes a private L1 cache, while L2 or L3 caches may be shared among cores. Cache coherence protocols like MESI (Modified, Exclusive, Shared, Invalid) or MOESI are used to maintain consistency across caches [2].

For example, in a GEMM (General Matrix Multiply) task within a machine learning model,

matrix data is cached and shared efficiently among cores, enabling fast computation during neural network inference [4]. The high-speed interconnects (often implemented as crossbar switches) support concurrent memory access, which enhances performance but adds complexity due to the overhead of maintaining cache coherence [1].

Tightly coupled architectures are compact and power-efficient, making them ideal for real-time embedded applications. In an autonomous vehicle, for instance, such processors allow cores to immediately share data from radar and camera sensors, enabling quick obstacle detection and safe navigation. Similarly, embedded smart cameras use tightly coupled cores to perform parallel multimedia decoding tasks within milliseconds [3].

#### 4.1.2 Loosely Coupled Processors

Loosely coupled processors, by contrast, give each core its own private memory. Cores communicate not through shared memory but via message-passing mechanisms such as Networks-on-Chip (NoC) or external interconnects like Ethernet [1]. An intuitive analogy is that each core is like an independent worker using their own notebook, sending messages only when necessary.

This design simplifies memory management because cache coherence is not required, but it introduces the need for explicit communication protocols, such as the Message Passing Interface (MPI) [5]. The NoC interconnect—often organized in mesh or torus topologies—enables scalable communication among cores but adds routing and latency overhead [4].

In a loosely coupled GEMM processor, each core processes a part of the matrix using its local memory. Inter-core communication is handled by the NoC, which routes partial results between cores as needed [4]. This is particularly advantageous in scientific simulations or cloud-based applications, where computation is distributed over many nodes. In a smart city IoT network, for instance, loosely coupled cores might each process local data—such as traffic or air quality metrics—and share only aggregated insights to a central server, supporting large-scale, distributed analytics.

#### 4.1.3 Architectural Comparison

The primary architectural difference between tightly and loosely coupled systems lies in memory organization:

- Tightly coupled processors use a centralized shared memory, which simplifies data access and synchronization but can create contention and requires complex cache coherence mechanisms.

- Loosely coupled systems rely on private memory per core, removing the need for coherence but requiring explicit communication and incurring higher latency due to routing overhead.

Tightly coupled architectures are best suited for real-time, latency-sensitive tasks and compact single-chip systems, leveraging high-speed cache hierarchies. Loosely coupled designs offer better scalability and modularity, making them ideal for parallel, distributed workloads across large systems [2, 4, 5].

## Tightly Coupled vs Loosely Coupled Architectures

Figure 1: Architectural overview of tightly coupled and loosely coupled multicore processors. If this figure is adapted or inspired by prior work, cite the original source accordingly (for example: adapted from [1]).

## 4.2 Data Rate

Data rate — the speed at which data is transferred between processing elements — plays a crucial role in determining parallel performance. It affects how efficiently tasks are distributed and how quickly results are produced, especially in compute-intensive operations.

**Tightly Coupled Processors:** Tightly coupled systems offer high data rates thanks to their centralized shared memory and low-latency interconnects. Cores can directly access and exchange data without the need for explicit transfer protocols, resulting in rapid data movement within the chip [2]. In GEMM tasks, for example, this architecture allows large matrices to be cached and shared efficiently, with crossbar switches or ring networks facilitating high-throughput communication. Cache coherence protocols such as MESI maintain data consistency across caches with minimal overhead [5]. These characteristics make tightly coupled systems well-suited for real-time embedded applications, such as sensor data processing in smart devices, where fast and consistent data access is essential.

**Loosely Coupled Processors:** Loosely coupled systems typically achieve lower data rates due to their use of message-passing communication across distributed memory structures. Data is transferred over a Network-on-Chip (NoC) or external interfaces like Ethernet, introducing routing delays and bandwidth limitations [4]. In GEMM workloads requiring frequent data exchange, the NoC can become a bottleneck, limiting effective data rates to 2–5 GB/s depending on congestion and network design [4]. Despite the lower throughput, this architecture is advantageous for scalable systems such as distributed IoT networks, where independent nodes handle localized computation and only periodically communicate results — prioritizing modularity and scalability over raw speed.

### 4.3 Type of Network

The communication network determines how processor cores exchange data and plays a critical role in shaping system performance and scalability.

**Tightly Coupled Processors:** Tightly coupled systems typically employ high-speed, low-latency on-chip interconnects such as buses, ring topologies, or crossbar switches [1]. These interconnects facilitate direct communication and simultaneous access to shared memory, which is essential for high-performance tasks like GEMM [2]. For example, crossbar switches allow parallel memory access by multiple cores, minimizing communication delays. However, these tightly integrated networks are generally limited to single-chip configurations, making them less scalable as the number of cores grows [5]. In time-sensitive embedded systems like autonomous vehicles, such networks enable fast, synchronized data exchange critical for functions like obstacle detection.

**Loosely Coupled Processors:** Loosely coupled systems rely on message-passing communication over scalable interconnects, such as mesh or torus topologies in Network-on-Chip (NoC) architectures or external links like Ethernet [1]. These networks support distributed memory systems and allow cores to operate independently. In applications such as distributed GEMM acceleration, mesh-based NoCs enable scalable inter-core communication across multiple nodes [4]. However, the routing and synchronization overhead in these networks introduces higher latency compared to tightly coupled interconnects, which can affect real-time performance [5]. Despite this, they are well-suited for large-scale applications like smart city IoT infrastructures, where scalability is a priority.

**Comparison:** Tightly coupled processors utilize low-latency on-chip interconnects like crossbar switches, excelling in applications needing rapid, synchronized data exchange, such as robotic control [2]. Loosely coupled processors employ scalable NoC or external networks, offering flexibility for distributed systems like IoT networks, but with increased latency [4].

### 4.4 Data Communication

In tightly coupled systems, communication is typically achieved through shared memory, where all cores access a common memory space using high-speed interconnects, such as buses or crossbar switches [1]. This setup allows for low-latency and deterministic data exchange, making it ideal for time-sensitive applications like real-time robotics, signal processing, or neural network inference. For example, in the Loki architecture, cores communicate through fast on-chip networks and share caches, enabling tasks such as convolutional neural networks (CNNs) to process data in parallel with minimal delay [2]. The use of interconnects in such systems supports efficient synchronization and fine-grained communication, albeit with challenges related to cache coherence and scalability as core count increases [1, 2].

In contrast, loosely coupled systems rely on message-passing between cores, each of which has private memory. Communication is typically handled using Network-on-Chip (NoC) or even external network protocols like MPI (Message Passing Interface) [1, 4]. This architecture favors modularity and fault tolerance, as each core operates largely independently and communicates explicitly with others. For instance, in the MACO architecture, developed to accelerate matrix operations, tiles send and receive data using a distributed NoC, allowing efficient partitioning of

workloads like GEMM (General Matrix-Matrix Multiplication) [4]. While this model enhances scalability and avoids cache coherence issues, it introduces higher communication latency and demands greater programming effort to coordinate data exchange [3,5].

Overall, tightly coupled systems prioritize speed and low-latency communication, making them suitable for compute-bound and time-critical tasks. Loosely coupled systems, on the other hand, offer scalability and resilience, making them well-suited for distributed and data-intensive applications such as smart infrastructure or large-scale IoT networks [1,4,5].

## 4.5 Advantages

### 4.5.1 Tightly Coupled Processors:

- **Fast Communication:** The shared memory architecture enables rapid data access and synchronization, minimizing communication delays. This allows cores to share data without explicit transfers, critical for applications requiring real-time responsiveness, such as video processing or embedded systems. The low-latency interconnects ensure that data is available to all cores almost instantaneously, enhancing system efficiency for tightly integrated tasks [1].

- **High Performance for Integrated Tasks:** Tightly coupled cores excel in compute-intensive tasks like General Matrix Multiply (GEMM), where rapid data exchange supports high-throughput computing. For example, in machine learning applications, such as neural network training, tightly coupled systems efficiently handle large matrix operations by leveraging shared memory to minimize latency. This performance advantage is particularly evident in single-chip systems where cores work collaboratively on shared datasets [2].

- **Efficient Resource Utilization:** Shared memory reduces redundancy, as all cores access a common memory pool, optimizing storage efficiency. This eliminates the need for duplicate data copies across cores, reducing memory footprint and enabling cost-effective hardware designs for applications like real-time analytics or multimedia processing, where memory efficiency is crucial [5].

- **Simpler System Design:** The centralized architecture simplifies hardware design by using a single memory controller and shared interconnects. This reduces the complexity of integrating multiple cores on a single chip, making tightly coupled systems easier to design and manufacture for applications requiring compact, high-performance solutions, such as mobile devices or embedded controllers [3].

### 4.5.2 Loosely Coupled Processors:

- **Scalability:** The distributed memory architecture allows loosely coupled systems to scale to large numbers of processors or nodes, making them ideal for large-scale computing environments. For instance, in distributed GEMM tasks, cores can be added to handle larger datasets without significant redesign, supporting applications like big data analytics or cloud computing clusters where system size must grow dynamically [4].

- **Fault Tolerance:** Independent cores with private memories ensure that a failure in one module does not disrupt the entire system. This resilience is critical in distributed systems, such as data centers, where a single node failure must not compromise overall functionality. For example, in cloud computing, loosely coupled systems can continue operating even if one server fails, ensuring high availability [1].

- **Flexibility:** Loosely coupled systems support heterogeneous architectures, accommodating diverse workloads across different cores or nodes. This allows integration of specialized processors (e.g., GPUs alongside CPUs) in applications like scientific simulations, where different tasks require varying computational capabilities, enhancing system adaptability [4].

- **Modularity and Incremental Expansion:** The distributed design enables easy addition or removal of cores, enhancing system adaptability. This modularity supports incremental upgrades in distributed computing environments, such as adding new nodes to a cluster for increased processing power, making loosely coupled systems suitable for evolving workloads in cloud or grid computing. Incremental hardware expansion is a particular strength of loosely coupled designs, allowing systems to grow after initial deployment with minimal redesign [5].

## 4.6 Disadvantages

### 4.6.1 Tightly Coupled Processors:

- **Limited Scalability:** Memory contention and interconnect bandwidth constraints restrict the number of cores that can be effectively integrated. As core count increases, competition for shared memory access leads to bottlenecks, reducing performance in large-scale systems. For example, in high-core-count processors, the shared bus may become saturated, limiting scalability for applications like large-scale simulations [1].

- **Complex Cache Coherence:** Maintaining data consistency across shared memory requires sophisticated cache coherence protocols, increasing design complexity and computational overhead. Protocols like MESI or MOESI involve frequent cache updates, which can degrade performance in applications with high data contention, such as multi-threaded database processing, where cores frequently access shared data [2].

- **Single Point of Failure:** The shared memory represents a single point of failure, where a memory or interconnect issue can disrupt the entire system. For instance, a failure in the memory controller can halt all core operations, making tightly coupled systems less reliable for critical applications like aerospace control systems, where downtime is unacceptable [5].

- **Higher Power Consumption:** Frequent shared memory access and coherence protocols increase power consumption, particularly as core count grows. The energy cost of maintaining cache coherence and high-speed interconnects makes tightly coupled systems less suitable for energy-constrained environments, such as mobile devices or battery-powered embedded systems [3].

#### 4.6.2 Loosely Coupled Processors:

- **Higher Communication Latency:** Message passing introduces significant latency, reducing efficiency in tasks requiring frequent data exchange. For example, in GEMM tasks with high inter-core communication, the NoC's routing overhead can slow down processing, making loosely coupled systems less effective for real-time applications like video streaming or online gaming [4].

- **Complex System Design:** The need for explicit communication protocols, such as MPI, and network management increases design and programming complexity. Developers must handle data transfers and synchronization manually, which complicates software development for applications like distributed machine learning, where coordination between nodes is frequent [1].

- **Network Bottlenecks:** Scalable networks like NoC may face congestion in high-communication scenarios, limiting performance. For instance, in data-intensive applications like real-time analytics, network congestion can delay data transfers, reducing system responsiveness compared to tightly coupled systems [4].

- **Resource Redundancy:** Private memories lead to duplicated data storage across cores, increasing memory requirements and reducing efficiency. In applications like big data processing, where large datasets are distributed across nodes, this redundancy can increase hardware costs and complexity, as each core maintains its own data copy [5].

### 4.7 Trade-offs in Tightly Coupled and Loosely Coupled Systems

#### 4.7.1 Performance and Efficiency

Tightly coupled processors excel in compute-intensive tasks requiring frequent data sharing, such as General Matrix Multiply (GEMM). In machine learning applications like neural network training, these systems leverage shared memory and low-latency interconnects to achieve high throughput. Bates et al. [2] demonstrate that optimized GEMM implementations on tightly coupled cores can reduce execution time by up to 30% compared to single-core systems, enabling efficient matrix processing in deep learning tasks such as image recognition or natural language processing. Real-time systems, like autonomous vehicle control, also benefit from their rapid data processing capabilities, meeting stringent latency requirements [2]. However, performance degrades as the number of cores increases, due to memory contention and coherence overheads, which limit scalability [5]. Additionally, shared memory access and coherence protocols result in higher power consumption [1] and reduced fault tolerance, as errors in one core can affect the entire system [1].

Loosely coupled processors are better suited for distributed workloads with minimal inter-core communication, such as big data analytics or scientific simulations. Sui et al. [4] show that their loosely coupled multi-core architecture designed for GEMM can efficiently process independent data chunks across nodes, offering scalability for large datasets. In cloud-based analytics, loosely coupled systems distribute computation across many nodes, improving throughput for tasks like log analysis or genomic sequencing. For distributed GEMM tasks, each core handles a subset of the matrix and communicates results via a Network-on-Chip (NoC), which enables scalability

but introduces higher latency [5]. These systems also benefit from modular power distribution, although communication overheads via the NoC can offset some energy savings [4]. Their decentralized nature increases fault tolerance, as failure in one node typically does not disrupt the entire system [4].

#### 4.7.2 Programming Complexity

Tightly coupled systems support simpler programming models such as OpenMP, which abstract communication and simplify synchronization. For instance, developers can parallelize loops in GEMM implementations using OpenMP directives, facilitating shared memory access. This is particularly useful in image processing applications, where convolution operations can be efficiently distributed across cores. Bates et al. [2] emphasize that OpenMP reduces development time and complexity, making it accessible even for developers with limited experience in parallel programming—an important benefit for embedded applications with tight development cycles.

In contrast, loosely coupled systems require more complex programming frameworks like the Message Passing Interface (MPI), which involve explicit control over data transfer and synchronization. MPI is often used in scientific simulations, such as climate modeling, where programmers must manually partition data and manage inter-node communication. While this enables high scalability, it significantly increases development time and the potential for programming errors. Sui et al. [4] note that managing NoC-based communication in distributed machine learning tasks contributes to performance overheads and a steep learning curve.

#### 4.7.3 Cost Implications

Tightly coupled processors typically incur higher hardware costs due to the need for complex shared memory controllers, cache coherence mechanisms (e.g., MESI), and high-speed interconnects like crossbar switches. These design features increase manufacturing complexity, especially in embedded systems such as automotive controllers. However, their simpler programming model (e.g., OpenMP) reduces software development effort and associated costs [2]. For real-time analytics, their compact, integrated design can minimize the need for external hardware, partially offsetting the initial hardware expenses [5].

Loosely coupled processors generally have lower per-node hardware costs, thanks to their modular architecture where each node operates with its own local memory and communicates via a scalable NoC. This makes them suitable for incremental expansion, as seen in cloud computing clusters. However, the complexity of programming with MPI introduces higher software development costs, requiring specialized knowledge to manage data exchange and synchronization. Moreover, in large-scale deployments, the redundancy of memory across nodes can further increase total system costs, especially in data-heavy applications like genome analysis [4].

Tightly and loosely coupled systems each present distinct trade-offs in performance, scalability, programming complexity, and cost. Tightly coupled architectures are well-suited for low-latency, compute-intensive tasks but face scalability and power challenges. In contrast, loosely coupled designs excel in distributed applications with high scalability and fault tolerance but require complex programming models and may suffer from communication overheads. The choice between the two depends on workload characteristics and system requirements. Table 1 summarizes the main architectural differences to support design decisions.

## 5 Examples of Tightly and Loosely Coupled Systems in Computing

The rise of multicore processors has significantly enhanced computing capabilities across a wide range of domains, including machine learning, real-time robotics, distributed IoT systems, and scientific simulations. This section illustrates how the concepts introduced earlier translate into real-world implementations by presenting two representative architectures: the tightly coupled **Loki** processor and the loosely coupled **MACO** architecture. By examining their design, usage scenarios, and performance characteristics, we highlight how architectural choices influence efficiency, scalability, and applicability. These examples make the abstract concepts of coupling more tangible and provide practical insights for embedded systems and robotics.

### 5.1 Tightly Coupled Cores: Example – Loki Architecture

A well-known representative of tightly coupled architectures is the **Loki processor**, a homogeneous many-core system designed for high energy efficiency and extremely low-latency communication among its cores. Loki emphasizes shared memory integration and compact interconnects, which allow groups of cores to work closely together. This design makes it suitable for performance-critical tasks where rapid data sharing and synchronization are essential.

As reported by Bates et al. [2], Loki demonstrates the benefits of tightly coupled systems in compute-intensive and real-time contexts. For example, in convolutional neural network (CNN) prototyping, Loki achieves fast inference by minimizing communication overhead between layers. In robotic control, its shared memory enables near-instantaneous access to sensor data, supporting quick reactions such as obstacle detection or trajectory adjustments. This makes Loki an effective solution for embedded applications that require deterministic performance, such as autonomous vehicles or surveillance drones. In these cases, tightly coupled cores allow different subsystems (e.g., vision, navigation, and control) to share data with minimal delay, improving both safety and responsiveness.

### 5.2 Loosely Coupled Cores: Example – MACO Architecture

An illustrative example of a loosely coupled system is the **MACO architecture**, which organizes multiple cores with independent local memory, connected through a scalable Network-on-Chip (NoC). Unlike Loki, MACO does not rely on a single shared memory pool. Instead, each core processes data independently and communicates results via message passing. This approach eliminates cache coherence concerns, but introduces higher communication latency.

Sui et al. [4] show that MACO excels in **General Matrix Multiplication (GEMM)** workloads and other data-parallel tasks where computation can be distributed into independent chunks. Its scalability makes it particularly useful in large-scale scientific simulations, embedded AI workloads, and IoT networks. For instance, in a smart city application, individual MACO cores can process localized data such as traffic density or air quality, sharing only aggregated summaries with a central node. This not only reduces communication bottlenecks but also improves fault tolerance, since failure of one core does not halt the entire system. Furthermore, loosely coupled systems like MACO enable **incremental hardware expansion**, meaning new cores or nodes can be added after deployment—a flexibility that tightly coupled systems typically cannot offer.

### 5.3 Comparative Insights

The two examples highlight the contrasting strengths of tightly and loosely coupled architectures. Loki’s design demonstrates how shared memory and low-latency interconnects deliver rapid, synchronized processing. This makes it highly effective for tasks where timeliness is critical, such as real-time object detection in autonomous vehicles or motion planning in robotic manipulators [2]. Its efficiency comes from reducing the cost of communication between cores, allowing them to collaborate seamlessly.

MACO, on the other hand, shows how a loosely coupled architecture can scale to large, distributed workloads. By leveraging its NoC-based communication and decentralized memory, MACO achieves high throughput for matrix operations, cloud analytics, or IoT applications [4]. However, this comes at the expense of higher communication latency, which makes it less suitable for hard real-time scenarios. Still, the ability to expand hardware incrementally and to maintain operation even if individual nodes fail gives loosely coupled systems a resilience that tightly coupled designs often lack.

These examples underscore the principle that architectural suitability depends on application requirements. Tightly coupled systems like Loki are preferred in domains requiring **low latency, synchronized execution, and compact integration**, while loosely coupled systems like MACO are advantageous when **scalability, modularity, and fault tolerance** are the primary concerns. Together, they provide a comprehensive view of how multicore architectures can be tailored to meet diverse computational needs, from embedded robotics to large-scale distributed computing.

## 6 Architectural Considerations for Embedded System Design

As embedded systems and robotics continue to evolve, selecting the appropriate multicore architecture—tightly coupled or loosely coupled—requires careful consideration of system-level constraints such as latency, memory access patterns, energy efficiency, and fault tolerance. While Sections 4 and 5 discussed technical attributes and representative case studies, this section extends the analysis by examining how these architectural trade-offs directly shape embedded system design choices. The focus lies on identifying key constraints, memory and communication strategies, application-specific requirements, and the potential for hybrid approaches.

### 6.1 Design Constraints in Embedded Systems

Embedded systems, particularly in robotics or autonomous vehicles, must often meet hard real-time deadlines while operating under strict power and size constraints. Tightly coupled multicore systems are typically favored in such scenarios due to their low-latency memory access and deterministic behavior enabled by shared memory and high-speed interconnects [1,2]. For example, the Loki architecture demonstrates how cores can exchange sensor data within milliseconds, enabling robotic arms to adjust their movements in real time in response to environmental inputs [2]. This rapid communication is critical for safety-related applications such as collision avoidance, object manipulation, or real-time SLAM (Simultaneous Localization and Mapping).

By contrast, embedded systems deployed in distributed environments—such as smart cities, in-

dustrial monitoring, or large-scale IoT networks—require scalability and fault isolation. Loosely coupled processors are well-suited for these scenarios due to their modularity and resilience. As shown by the MACO architecture [4], each processing tile can operate on localized workloads independently and communicate results via a Network-on-Chip (NoC). In a practical deployment, loosely coupled nodes could handle sensor fusion from hundreds of IoT devices across a factory floor or city district. Failures are contained to individual modules, and additional cores can be integrated incrementally to expand system capabilities without redesigning the entire architecture [4].

## 6.2 Memory and Communication Trade-Offs

One of the central design decisions in embedded systems is the trade-off between shared and distributed memory. Tightly coupled systems with shared memory simplify software development, particularly for compute-intensive tasks such as matrix multiplication or convolutional filtering, by supporting parallel programming models like OpenMP [2, 3]. These abstractions allow developers to focus on algorithm design rather than communication details.

Loosely coupled systems, however, provide stronger memory locality and avoid cache coherence overhead, but they require explicit communication through protocols like MPI. This increases programming complexity, as developers must manually manage data transfers and synchronization across nodes [1, 3, 5]. The trade-off is therefore between developer convenience and system scalability: tightly coupled architectures optimize for latency and throughput, while loosely coupled designs prioritize modularity, isolation, and incremental growth.

## 6.3 Application-Centric Architecture Choice

Bates et al. [2] emphasize that applications such as neural network inference benefit from tightly coupled designs, where frequent data reuse across layers is supported by shared memory. In contrast, MACO’s tile-based instruction set demonstrates how loosely coupled architectures can distribute GEMM operations effectively across multiple cores, achieving high throughput in large batch-processing tasks [4].

A concrete comparison illustrates this divergence: a robotic vacuum cleaner navigating a dynamic environment requires immediate obstacle detection and path adjustment, favoring tightly coupled cores with shared caches for deterministic performance [2]. Conversely, a smart grid analyzing power consumption across multiple neighborhoods benefits from a loosely coupled approach, where independent nodes aggregate and periodically exchange data. This distributed model enhances scalability and fault isolation, ensuring the system remains operational even if individual modules fail [4, 5].

## 6.4 Toward Adaptive and Hybrid Solutions

Although most literature distinguishes between tightly and loosely coupled architectures, the emerging trend is toward hybrid solutions that integrate both. As highlighted in [2] and [4], the Loki and MACO processors each optimize for specific domains, underscoring that no single

approach is universally optimal. Future embedded systems may therefore combine tightly coupled cores for time-critical operations with loosely coupled tiles or accelerators for background analytics, all integrated within a single system-on-chip (SoC). Such adaptive architectures balance latency, scalability, and resilience, offering designers greater flexibility in meeting diverse application demands across robotics, IoT, and smart infrastructure.

| Aspect                            | Tightly Coupled                                                                                        | Loosely Coupled                                                                                           |

|-----------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| <b>Structure and Architecture</b> | Shared memory, crossbar/ring interconnects, cache hierarchy [1, 2]                                     | Private memories, message-passing via NoC (mesh/torus), modular design [1, 4]                             |

| <b>Data Rate</b>                  | High, due to centralized shared memory and low-latency interconnects [2]                               | Lower, limited by routing delays and message-passing overhead [4]                                         |

| <b>Type of Network</b>            | On-chip bus, ring, or crossbar (fast but less scalable) [2]                                            | Network-on-Chip or Ethernet (scalable but higher latency) [4]                                             |

| <b>Data Communication</b>         | Implicit through shared memory, low-latency access [2]                                                 | Explicit message-passing, requires MPI or similar protocols [4, 5]                                        |

| <b>Advantages</b>                 | Fast communication, high performance for integrated tasks, efficient memory usage [2, 3]               | Scalable, fault-tolerant, flexible, supports heterogeneous and incremental hardware expansion [4, 5]      |

| <b>Disadvantages</b>              | Limited scalability, complex cache coherence, single point of failure, higher power consumption [1, 2] | Higher communication latency, complex design/programming, network bottlenecks, resource redundancy [4, 5] |

| <b>Performance</b>                | Excels in compute-intensive and real-time tasks (e.g., robotics, CNN inference) [2]                    | Effective in distributed, data-parallel workloads (e.g., IoT, GEMM, simulations) [4]                      |

| <b>Programming Complexity</b>     | Lower, OpenMP support for shared memory parallelism [2]                                                | Higher, MPI required for explicit communication and synchronization [1, 4]                                |

| <b>Power Efficiency</b>           | Higher power consumption due to coherence protocols and frequent memory access [1]                     | Distributed consumption across nodes; energy cost depends on NoC efficiency [4]                           |

| <b>Fault Tolerance</b>            | Limited, shared resources create single points of failure [1]                                          | High, independent modules isolate failures; resilient in distributed systems [4]                          |

Table 1: Comparison of tightly coupled and loosely coupled multicore architectures.

## 7 Conclusion

This seminar report has provided a comprehensive comparison of tightly coupled and loosely coupled multicore processors, explaining their architectural differences, performance characteristics, and application suitability within the context of embedded systems and robotics. Tightly coupled processors, with shared memory and low-latency interconnects, deliver high performance for compute-intensive tasks such as machine learning and real-time signal processing, as demonstrated in GEMM optimization studies [2]. However, their scalability and reliability are constrained by memory contention, complex cache coherence protocols, and single points of failure. In contrast, loosely coupled processors, with distributed memories and NoC-based communication, offer scalability, modularity, and fault tolerance for distributed applications such as cloud computing and big data analytics, though their higher communication latency limits real-time responsiveness [4].

These findings provide practical guidance for system design in embedded systems and robotics. Tightly coupled processors are well-suited for low-latency, real-time control tasks, such as autonomous navigation in drones or robotic manipulation, due to their speed and integrated memory access. Loosely coupled processors, on the other hand, are more appropriate for distributed sensor networks and IoT ecosystems, where scalability and resilience are essential. Selecting the appropriate architecture therefore requires a balanced evaluation of performance, scalability, energy efficiency, and fault tolerance, depending on application requirements.

### Key Takeaways:

- Use tightly coupled cores for latency-sensitive, compute-bound tasks such as real-time robotics.

- Prefer loosely coupled cores for scalable and fault-tolerant environments, including distributed IoT and cloud systems.

- Consider hybrid models for emerging domains such as autonomous vehicles or smart infrastructure.

Looking forward, research and industry trends point toward hybrid architectures that combine tightly and loosely coupled elements to achieve both high performance and scalability. For instance, integrating tightly coupled cores for safety-critical, time-sensitive operations with loosely coupled tiles for large-scale data processing may provide the best of both worlds in domains like smart cities and autonomous vehicles. Overall, this seminar highlights the importance of understanding multicore architecture paradigms and their trade-offs in order to design efficient, application-specific computing solutions for an increasingly parallel and interconnected computing landscape.

## References

- [1] Babasegun Adeleye and Salman Mohammed Jiddah. Analysis of parallel architectures: SIMD, tightly-coupled MIMD, and loosely-coupled MIMD, 2017.

- [2] Daniel Bates, Alex Bradbury, Andreas Koltès, and Robert Mullins. Exploiting tightly-coupled cores. In *Proceedings of the ACM/IEEE International Symposium on Computer Architecture (ISCA)*, 2014.

- [3] GeeksforGeeks.org. Difference between loosely coupled and tightly coupled multiprocessor system, 2024. Accessed: 2025-06-14. URL: <https://www.geeksforgeeks.org/difference-between-loosely-coupled-and-tightly-coupled-multiprocessor-system/>.

- [4] Bingcai Sui, Junzhong Shen, Caixia Sun, Junhui Wang, Zhong Zheng, and Wei Guo. Maco: Exploring GEMM acceleration on a loosely-coupled multi-core processor. *Journal of Parallel and Distributed Computing*, 2024.

- [5] TechDifferences.com. Difference between loosely coupled and tightly coupled multi-processor system, 2024. Accessed: 2025-06-14. URL: <https://techdifferences.com/difference-between-loosely-coupled-and-tightly-coupled-multiprocessor-system.html>.