# PLAYOUT - A Hierarchical Layout System

Bernd Schürmann

Gerhard Zimmermann

University of Kaiserslautern

D-67653 Kaiserslautern

## 1. Introduction

Very Large Scale Integration (VLSI) has become a technology of large economical importance. Mastering of this technology on one hand means the latest semiconductor processing technology, on the other hand computer aided design. Whereas the first is a problem for physics and chemistry, the progress in the second field results from large activities in electrical engineering and computer science. Although a large body of knowledge about solutions to partial problems exists, there is still a lack of combining all these results into integrated systems that are applicable to design very complex VLSI circuits. This is especially nowadays the case where we can see a shift from bottom-up to top-down design.

The PLAYOUT project aims at a solution of the systems problem, based on hierarchy, top-down planning and integrating design tools in a CAD framework which is based on an object-oriented data model and a net-based design flow model. PLAYOUT supports the physical design from behavioral synthesis to the generation of the mask data. PLAYOUT tries to enforce correctness, consistency, and completeness of designs in order to minimize checking requirements. PLAYOUT can be used as a fully automatic layout generator, but sufficient control is given to the designer to interact with the design process. Only the inclusion of designers experience will, in general, result in better than just acceptable layouts. Due to its strong focus on planning, PLAYOUT is also a useful *early design tool* for evaluating system and logic synthesis. The estimation component of physical circuit characteristics is the perfect back-end of the behavioral design phase.

Compared to existing layout tools without a planning component, we hope to achieve better results and less iterations in the design cycle. These advantages could be shown by a large test design of a circuit with nearly 300,000 standard cells using a prototype implementation of the PLAYOUT design system. We will use this example throughout this paper to explain the function of the PLAYOUT system.

This article emphasizes the system approach, the planning aspect, and the use of a hierarchy. New or improved algorithms will be of minor interest. Section 2 will give a short overview of the PLAYOUT design system. Section 3 will then describe our (top-down) design methodology while Section 4 will describe our main toolboxes in more detail. At the end, we will present some aspects of our CAD framework in Section 5 before we will conclude the paper by

addressing a large test design in Section 6.

## 2. System Overview

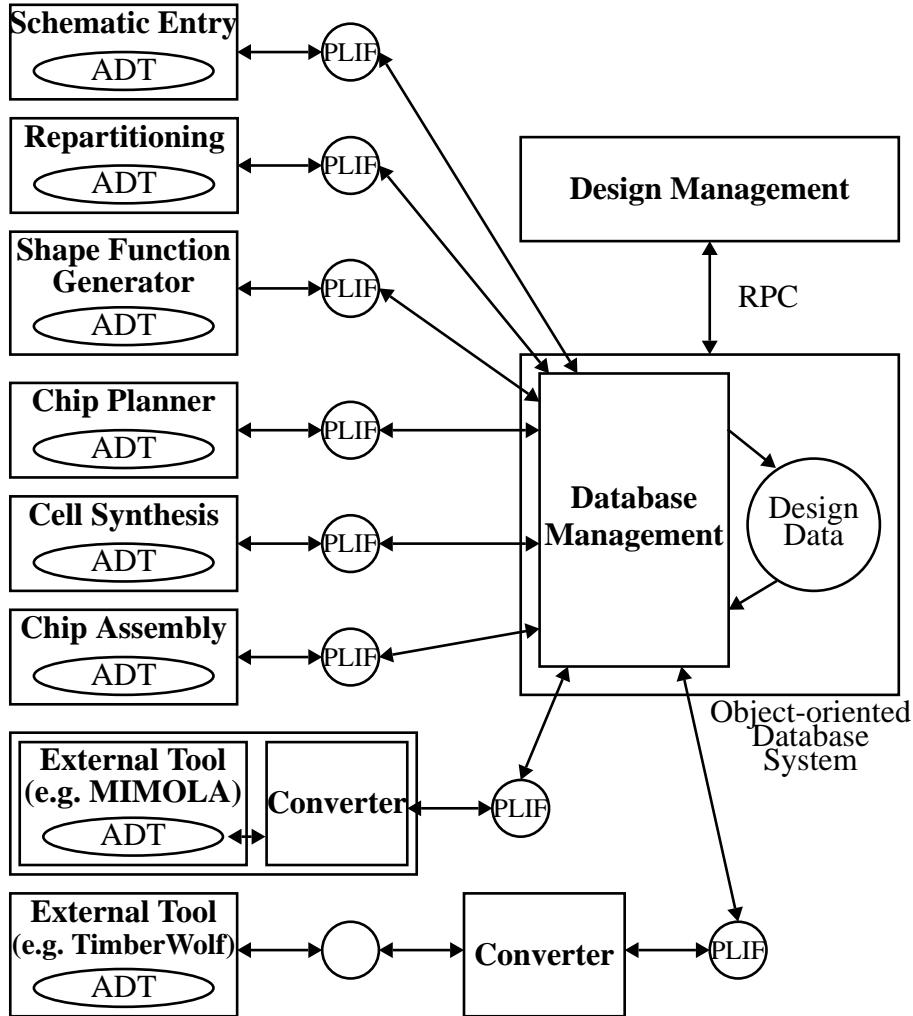

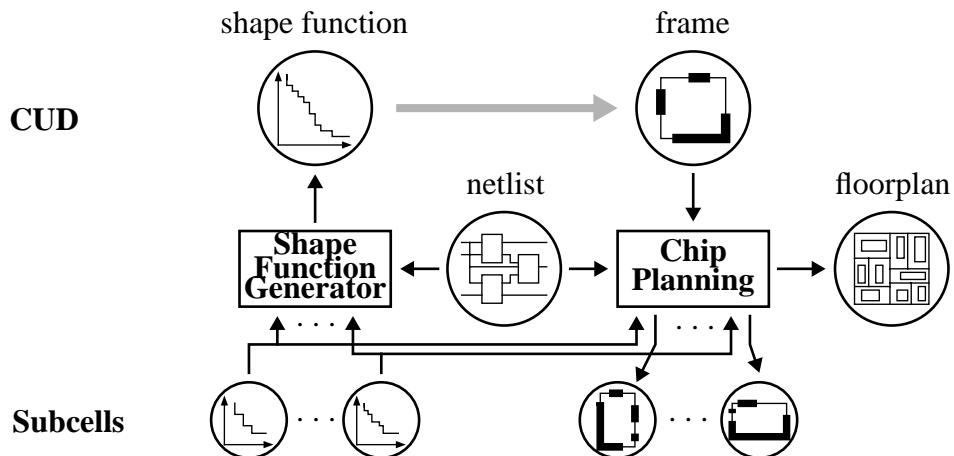

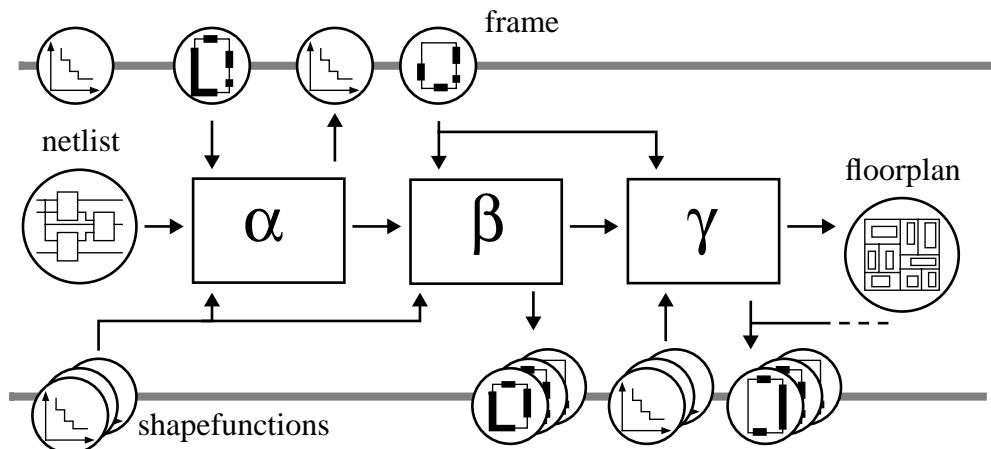

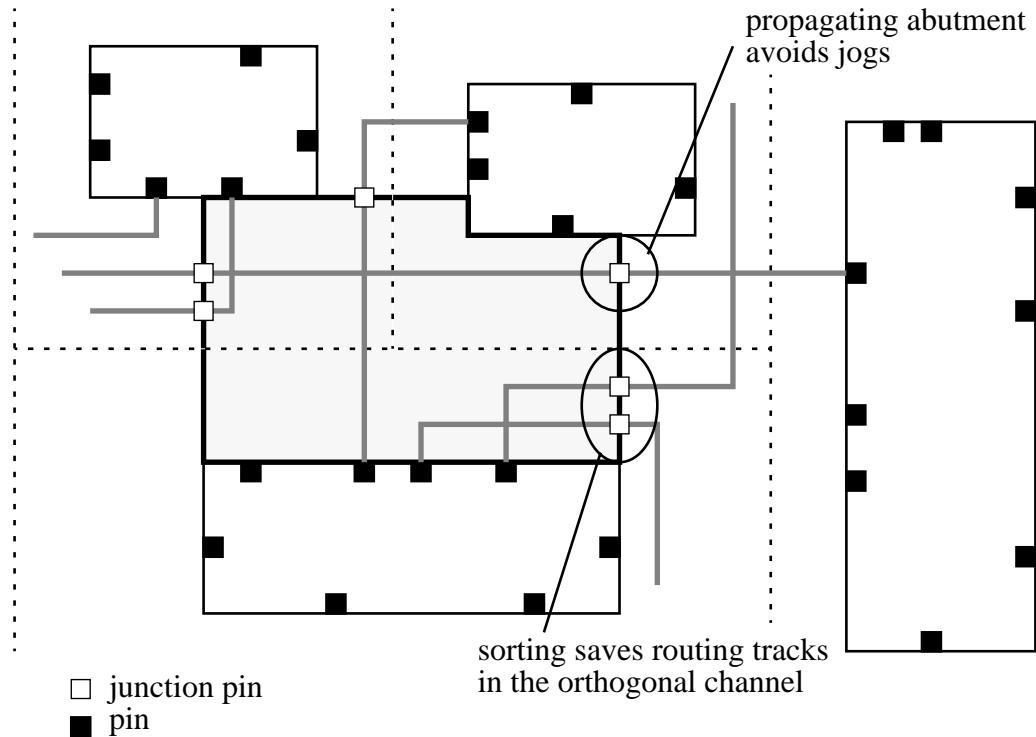

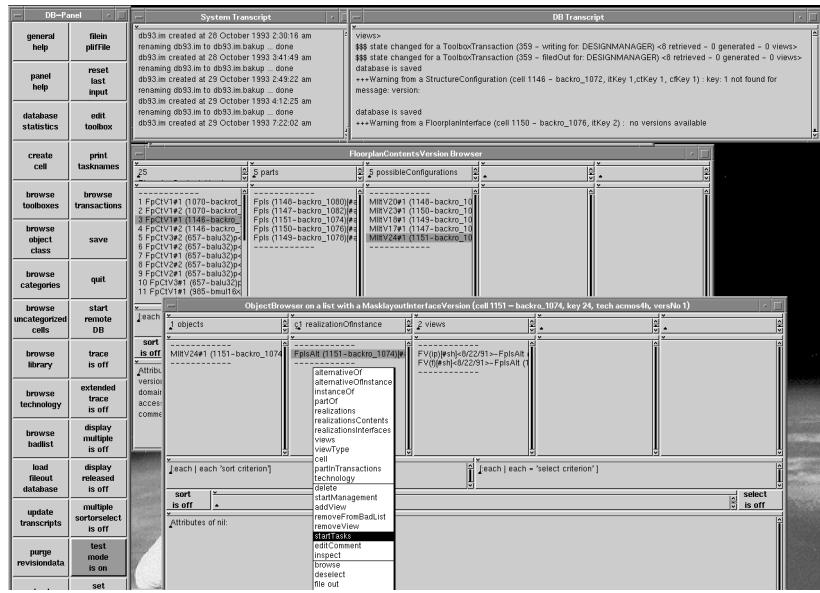

Figure 1 shows the PLAYOUT system architecture. The system is composed of independent toolboxes which perform the CAD functions. The toolboxes are separated because of different implementation languages and data structures. Most toolboxes have been implemented by our group but several foreign toolboxes like **TIMBERWOLF** [SeL87] and **MIMOLA** [Mar90, Zim88.1] have been adapted to the PLAYOUT system.

All toolboxes are loosely integrated in the PLAYOUT CAD framework **PLAYFRAME**. Each toolbox still has its central data structure and may have several tools that read and modify this structure. Design data are retrieved from the design database **PLAYBASE** in form of **PLIF** files and loaded into the local data structure [Sie89]<sup>1</sup>. External toolboxes are adapted by format converters so that the central design database sees a **PLIF** file interface only. For toolboxes for which we have access to the source code, the converter has been integrated into the toolbox. Otherwise the converter is a stand-alone interface.

Currently, each toolbox has its own user interface and controller. Control can also be passed down from the design manager [SpS88]. The design manager keeps track of the design progress and directs the database manager.

All design data are stored and administered by an object oriented non standard database. Each **PLIF** file is composed of a set of design objects that either represent the inputs or the results of a design step in a toolbox. The database manager composes and partitions these files for every toolbox application. The database stores all relations between complex design objects while the primitive design data are stored in the regular file system. The database has exclusive access to these files.

This structure is very flexible, but still efficient. The set of toolboxes can be easily changed, tools can be added to each toolbox and toolboxes can be executed on different computer types. The communication through files can be carried over any LAN and distributed database implementations are possible. With todays databases the level of complex objects as primitives allows for sufficient response times. Design file composition and decomposition on the database side and interpretation and generation on the toolbox side create overheads that are in the same range as the tool execution times. This disadvantage is compensated by the flexibility which is especially valuable during the tool development and prototype phases. With progress in nonstandard database research this file/complex object principle can be replaced in order to reduce the overhead.

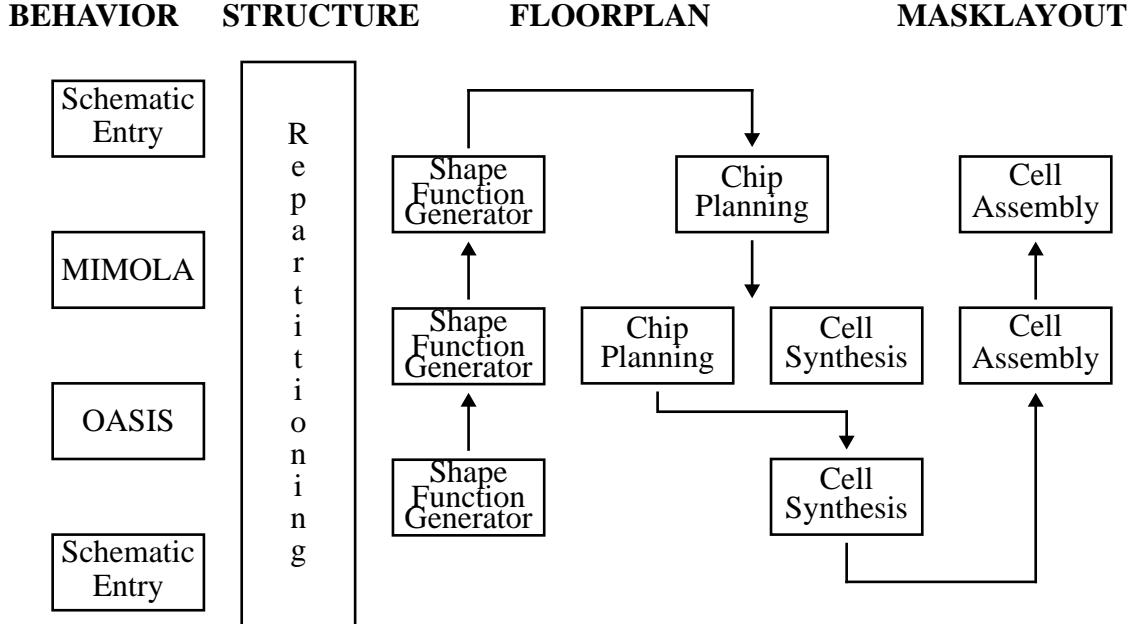

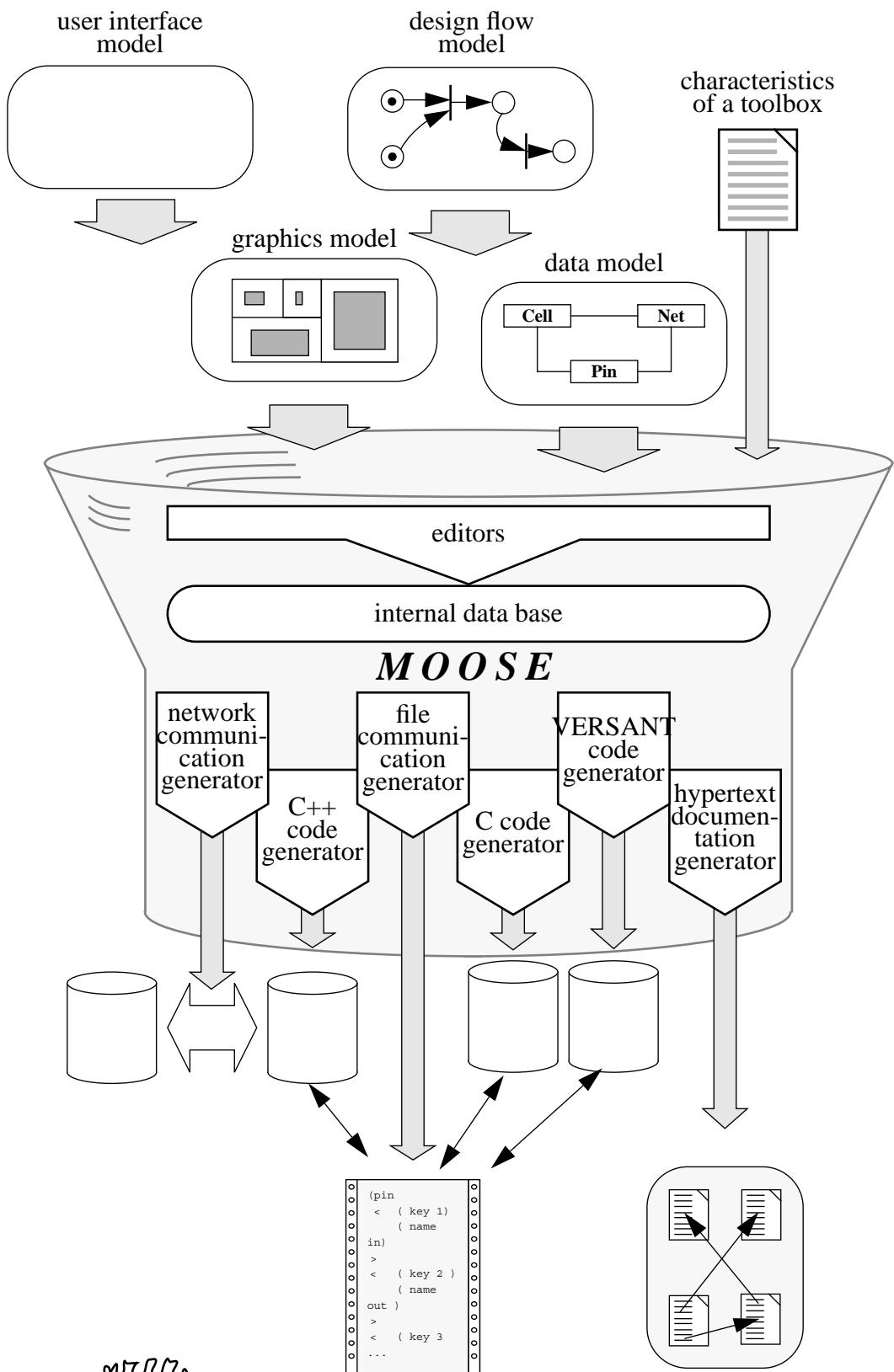

Figure 2 shows the dataflow between the toolboxes in a domain-level plane. Three domains

---

1. **PLIF** is a design data exchange format [Sie88] like **EDIF** [EDI87] and **VHDL** [HDL88]. In contrast to other exchange formats, **PLIF** has special language constructs for the physical planning phase.

Figure 1 *PLAYOUT design environment.*

All PLAYOUT toolboxes communicate via a design data base and ASCII (PLIF) files. External tools are adapted by converters. The design management is tightly coupled to the database via remote procedure call interface (RPC).

have been defined earlier [Zim81]: *behavior*, *structure* and the *physical domain*. The early design phases like *Hardware/Software Co-design*, *High-Level Synthesis*, and *Logic Synthesis* cover the left part of the plane while the physical design phase consisting of *Chip Planning*, *Place&Route*, and *Layout Synthesis* correspond to the right side. Verification and extraction steps as well as simulation and test aspects can be found in all design phases. We split the physical domain into *floorplan* and *masklayout* because of our chip planning emphasis.

Cells compose supercells or represent the complete system and are composed of subcells or are leaf cells. This relation defines an aggregation hierarchy which is represented by the levels in Figure 2. The levels can be defined as needed and the three levels in Figure 2 describe an example only.

In this figure, toolboxes, as for example the **CHIP PLANNER**, are placed on domain boundaries because they transform design data from one domain into another. Synthesis tools transform data of any domain into data of the next domain to the right, and extraction tools work in the opposite direction. Our **REPARTITIONER** is an alternative within a single domain. All toolboxes

Figure 2 *PLAYOUT* toolboxes.

This figure shows the most important *PLAYOUT* synthesis toolboxes. They perform the design over all domains, from behavior up to masklayout. Most toolboxes are used recursively at several hierarchy levels.

The arrows show the general physical design flow.

at least interact with two levels: the cell-under-design (CUD) and its subcells. At the top level the CUD is also called the system-under-design (SUD).

Figure 2 only shows the *PLAYOUT* tools which are most important for the physical top-down approach. Logic synthesis tools and module generators as well as the test environment are not part of *PLAYOUT* toolbox set but they are adapted with the *OASIS* design system [KBK90].

### 3. Design Methodology

Figure 2 can also be used to explain the design methodology of *PLAYOUT*. Starting point is a *behavioral description* of the system that has to be designed. This description is normally hierarchical and has to be transformed into a netlist. The synthesis will be performed by different toolboxes depending on the hierarchy level and the type of the behavioral description. The structure may be designed manually and entered via a schematic entry tool. However, this is the most time-consuming and error-prone possibility. More preferable is the usage of high-level synthesis tools at processor level, logic synthesis tools at RT level, and module generators for the basic functions. Structural data of standard functions may also exist in a library. Furthermore, a netlist may already exist from a previous implementation, perhaps with a different technology. Any mixture of sources is possible. A hierarchical netlist is complete if all basic functions are mapped onto layout primitives.

In *PLAYOUT* we use the high-level synthesis system *MIMOLA MSS II* [Mar90] that has been developed at the University of Dortmund. For all other circuit descriptions above and below

that hierarchy level we used a schematic entry tool for synthesizing our test designs in the past. Fortunately, we now can use the logic synthesis part of the **OASIS** design system instead of designing all these cells manually. Hardware/software co-design aspects are not considered by **PLAYOUT** until now.

In our running example that will be addressed in more detail at the end of the paper, 12 processing elements had been described behaviorally and synthesized with **MIMOLA**. A **MIMOLA**-to-**PLIF** interface that is integrated into **MIMOLA** generated the netlists at the processor level and a module list at the RT-level. In order to create the internal structure of the RT-modules, we used our schematic entry toolbox. Many of these RT-modules like multiplexers were refined in many hierarchy levels because of their high degree of regularity. At the lowest level the basic functions were mapped onto the commercial Siemens standard cell library **ACMOS4H**. At the upper-most hierarchy level, the twelve processors were connected to implement an asynchronous computing system by again using our schematic entry tool. We called the top-level circuit **XLII**.

The structure hierarchy normally shows partitions that resemble functional units as for example processors, adders, flip-flops, or gates. Rarely this partitioning is good for physical design. Physical design tools generate good results only if the number of subcells and the relative sizes of the subcells are within a certain range. Both conditions are violated by typical behavioral designs. In most cases, we have too many register transfer blocks as part of a processor netlist which may be large memories as well as small inverters. On the other hand, the register transfer blocks are built up by a deep hierarchy with few modules at each level. The cells at system level also consist of a small number of subcells only.

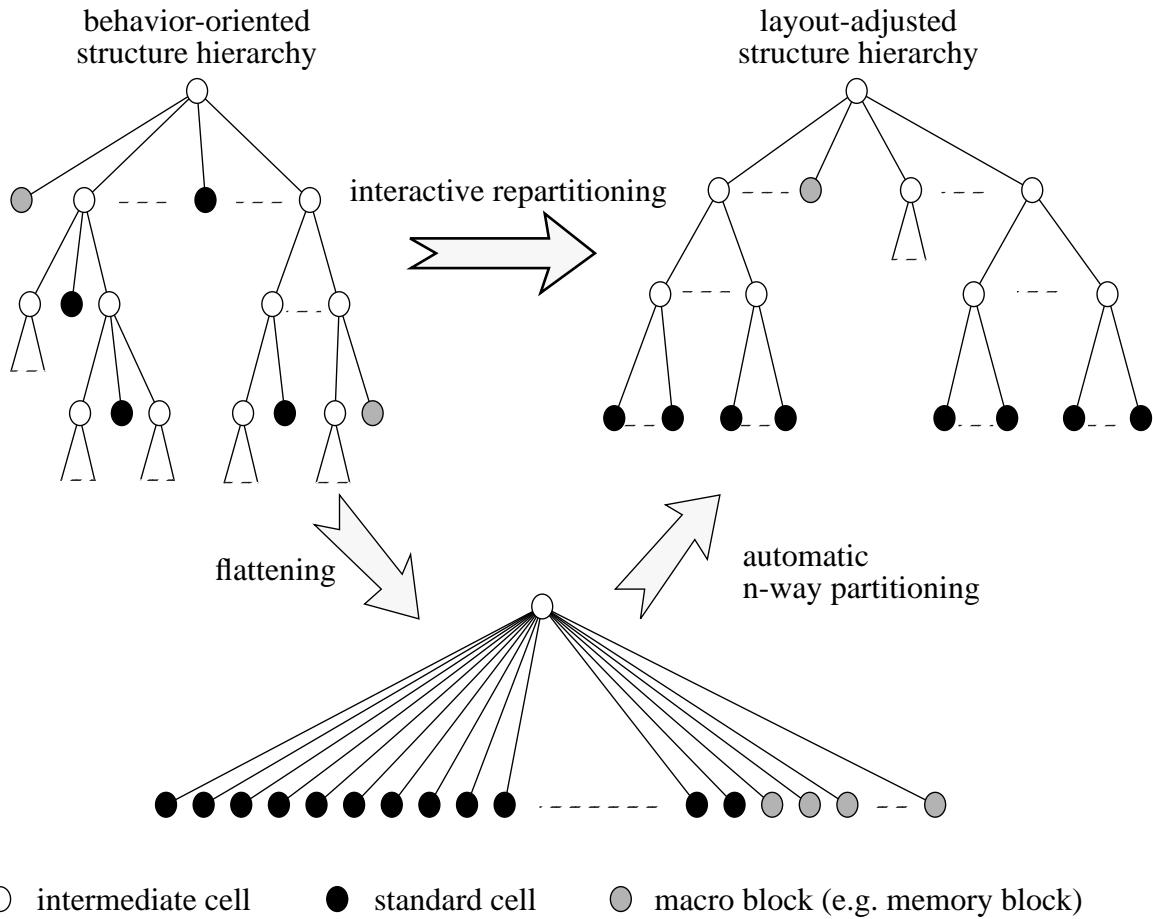

We call the modification of the behavior-oriented netlist hierarchy into a new hierarchy which fits to the physical design phase *repartitioning*. The automation of repartitioning is still an unsolved problem in VLSI design. A “flat” design with only one level of hierarchy would not solve the problem, because the complexities of the resulting placement and routing problems are too high to be feasible. Flattening the hierarchical netlist and then computing a new hierarchy from scratch (which is called *partitioning*) is neither a good approach because we then loose the whole regularity of the circuit. The modification of the hierarchy has to be as small as possible.

After repartitioning, hierarchical layout is generally done bottom-up. This means that first the layout primitives are combined to form detailed layouts of larger cells, these are then combined again until the chip is complete. At each level optimal layouts are sought, resulting in corresponding shapes and pin positions of each cell before it is used at the next higher level.

The problem of the bottom-up approach is that local decisions govern global ones. It is unlikely that different shapes (rectangles or more complex polygons) will fit together without wasted area. If the placement of subcells is optimized for high area utilization, wiring length and routing area at the higher hierarchy level will increase, as already has been observed by Breuer [Bre83].

Top-down chip planning tries to avoid wasted area and large signal delay times on higher (global) levels. Shapes are planned which will fit together with minimal dead area and which can be placed with minimal wiring length and total area at the higher levels. In order not to push the waste to the lower levels, a prediction of the influence of the global placement on the local subcell area and timing behavior is necessary. Specifically, this means a prediction of the influence of shape and pin locations on the characteristics of the subcells. The influence on the subcell area, which is already well examined, is generally expressed by shape functions. In contrast to that, the influence on the subcell's timing behavior is still an important research topic. The goal of chip planning is a trade-off between global and local aspects in order to find better layouts than with purely bottom-up methods.

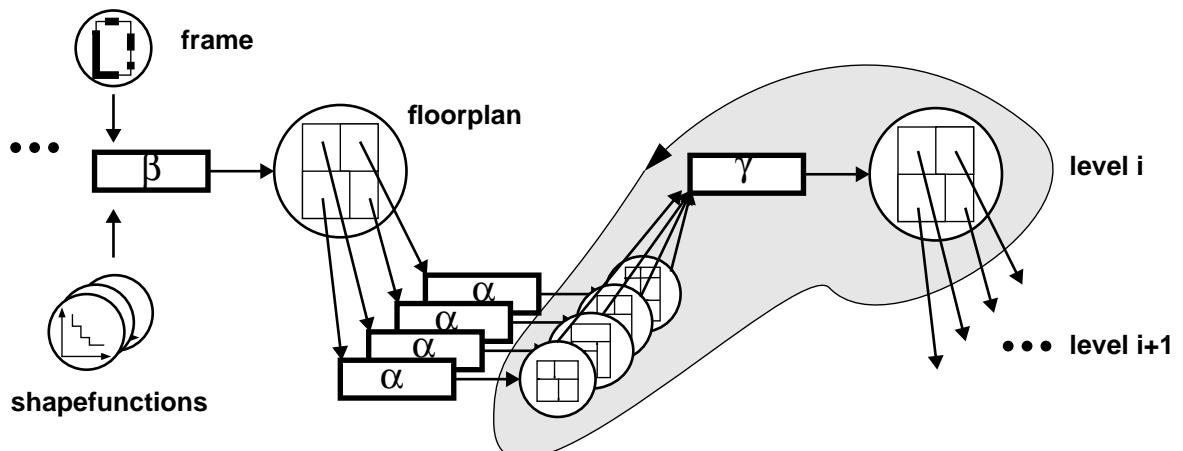

After repartitioning our area estimator called `SHAPE FUNCTION GENERATOR` calculates shape functions for all cells in the hierarchy. Inputs are the known shape functions of the used cell library (leaf cells) and the complete structural description. Figure 2 shows the bottom-up data-flow of three levels of shape function generation. Shape functions could be calculated in post-order in the hierarchy tree. This would cause many redundant calculations in the case of regularity. Redundancy is avoided by exploiting the cell type concept, i.e. by generating the shape functions for all non-leaf *cells* instead of the *instances* in the hierarchy tree. This has to be done in reverse topological order of the cell hierarchy (which can be extracted from the instance hierarchy). The chip level shape function is a prediction of the total chip area. If it fulfills the requirements, a suitable chip shape can be selected. Otherwise iterations through structural design and repartitioning may be necessary. This is a typical application of the `SHAPE FUNCTIONS GENERATOR` as an “early design tool”.

The `CHIP PLANNER` starts with a predicted shape of the chip and, if given, the pad positions. It tries to place the subcells in a slicing geometry [SzO80] such that the total area including inter-subcell-wiring becomes a minimum. The subcell shape functions and other constraints like maximum length of critical paths are taken into account. The `CHIP PLANNER` generates a floorplan consisting of the subcell placement and the assignment of the nets to wiring areas. No detailed routing is performed.

For each subcell the planned shape in the floorplan and the approximate pin positions (pin cost functions) are propagated to the next lower level. The `CHIP PLANNER` also generates a new CUD shape function, now based on the known placement and global routing. This shape function is more precise than the one generated by the `SHAPE FUNCTION GENERATOR`. It can be used for an adjustment step at the next higher hierarchy level.

The `CHIP PLANNER` is recursively called at the lower levels for all subcells again. The hierarchy tree can be traversed in breadth-first or depth-first manner. In case of a breadth-first traversal we have several choices. We can either plan all subcells independent of each other (sequentially or in parallel), or we can adjust the floorplan of the CUD after planning each subcell. This iterative planning/adjustment approach allows for a better response to deviations between planned and refined shapes and pin positions of the subcells. Our iterative approach is

called *Three-Phase Chip Planning*. However, this reduces the degree of parallelism and there still remains an ordering problem.

Better results are conceivable if all subcells of a CUD are planned in parallel with dynamical update of the CUD floorplan and communication between the neighbor subcells about shape and pin locations. This approach would probably generate the best results and could be distributed on parallel hardware. Still research is necessary to find the right communication parameters and control points and to study the convergence. One of the first parallel planning methods is described in [GlZ92].

In Figure 2 two planning levels are shown. Either more or fewer levels are possible, depending on the complexity of the total structure and the complexity which each toolbox can handle efficiently. The complexity is measured by the number of primitives that have to be placed in total or at each level. The `PLAYOUT CHIP PLANNER` works best with 30 to 80 subcells.

After chip planning the final mask layout has to be computed bottom-up with respect to the top-down computed floorplans. This phase is called *Chip Assembly* and it is split into *Cell Synthesis* and the following *Cell Assembly*. Cell synthesis is the link between the top-down planning phase and the bottom-up assembly phase. The input for cell synthesis is a frame and pin positions and is similar to the chip planning input. However, the cell synthesis step uses layout primitives (e.g. standard cells) and computes a final layout similar to cell assembly. In `PLAY-OUT` cell synthesis is currently restricted to memories and standard cells blocks to reduce the number of toolboxes to be supported.

Cell assembly uses the floorplan of the CUD and layouts of the subcells as input and computes the final layout of the CUD. Since we already performed a (top-down) planning step for the CUD, no placement has to be done as it is the case for pure bottom-up physical design. In our case, we take over the topology from the floorplan and only adjust the geometry with respect to the subcell layouts. The global routing information of the floorplan is refined by detailed routing. After successful detailed routing the mask layout is complete.

The hierarchy tree need not be balanced. We therefore may find cell synthesis and cell assembly steps at the same hierarchy level.

## 4. Toolboxes

After discussing the global design methodology we will now go into some more details of the toolboxes. Although `PLAYOUT` supports the whole VLSI design from behavior to layout, our main focus is the physical top-down chip planning phase. We will therefore concentrate on the toolboxes which cover this part of the design. These will especially be our area estimator called `SHAPE FUNCTION GENERATOR` and the `PLAYOUT CHIP PLANNER`. Besides these two toolboxes we will also describe the cell assembly based on the floorplan provided by the `CHIP PLANNER` and we will spend some place for addressing the repartitioning step. The latter is important for preparing the hierarchical netlist for the physical design phase.

The **PLAYOUT** front-end toolboxes which synthesize the netlist data from the behavioral description of a circuit have already been mentioned in the previous section. For this purpose we mainly use the **MIMOLA** synthesis system **MSII** from University of Dortmund and our own schematic entry toolbox for the manual synthesis steps. Recently, we also have access to the logic synthesis component of the **OASIS** design system from MCNC. Since both synthesis toolboxes have not been developed by our group and both do not belong to the main topic of this contribution we will not go into more detail of these design aspects.

For the remaining part of this contribution we assume that a hierarchical netlist is available no matter how it has been generated. However, the netlist hierarchy reflects the behavioral design. It therefore must be repartitioned to meet the requirements of the layout tools.

#### 4.1 Repartitioning

The goal in repartitioning is the generation of a suitable hierarchy for the physical design phase. A physical hierarchy has some hard and some soft conditions that have to be fulfilled. In this discussion we include levels beyond the chip level because very complex systems may require cabinets, racks, printed circuit boards (PCBs), multi chip carriers and chips.

Each of these levels has different requirements. Examples for hard conditions are the maximum number of slots in a rack, pins on PCB connectors, or of pads on a chip. Total power dissipation and chip area are other hard constraints.

On the chip soft conditions dominate. Currently we try to enforce the following:

- The number of cells placed by chip planning should be between 30 and 80. For a smaller number the flexibility may be too small to achieve dense placements. For larger numbers execution time would become too large for interactive design styles. For cell synthesis using standard cells the number should be between several hundreds and several thousands for similar reasons.

- The subcells of a CUD should not differ in area by more than a factor of 10. Especially for slicing geometries it is hardly possible to place very different cells together in a slice without stretching the smaller one beyond reasonable aspect ratios. On the other hand only few good placements exist for cells of equal shape. Thus a good distribution of subcell sizes in each CUD is an advantage.

- Functional hierarchies often display a high regularity by the use of standard functions. The RT-level, the gate level, and complex gate level are good examples. If we would repartition only with both objectives described above, most of this regularity would disappear and no standard function would remain on intermediate levels of the hierarchy. Loss of regularity results in a larger design task. The distribution of standard functions over many partitions would reduce the capability of manual inspection and comprehension of a layout. This would also reduce the possibilities of meaningful manual interactions and improvements.

- The number of nets between partitions should be minimized to the extent of what a good min-cut algorithm would achieve. This is necessary to reduce the overall wir-

ing length by pushing the dense wiring into cells at low levels of the hierarchy and thus small dimension.

- Considering timing conditions is very important. Experiments have shown that the structure hierarchy has a large impact on the timing behavior of the layout. Time-critical nets should therefore be limited to small cells, too. This should not only be achieved on the average but individually. One critical net with a long wiring length may determine the total systems performance.

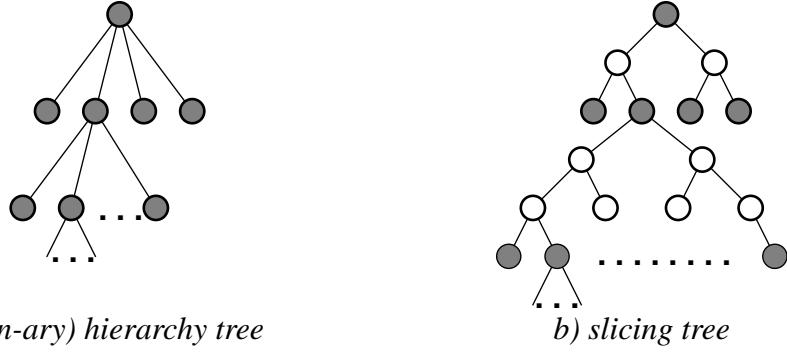

As we mentioned above, there are two alternative approaches to solve the problem (see Figure 3). The brute-force approach is to flatten the whole hierarchy and then to construct a new hierarchy from scratch by recursively applying an n-way partitioning algorithm. This method is depicted by the lower part of Figure 3.

Figure 3 Alternative repartitioning approaches

The problem for this approach is the large number of different objectives as described above. This number of conditions can be easily extended and it is difficult to merge all of them into a single cost function that would be necessary for the partitioning algorithm. Our idea therefore is to achieve the goals by small, local changes to the original hierarchy using an interactive repartitioning tool.

Opposite to the automatic n-way partitioning method would be a manual repartition

approach. The repartitioning tool would only keep track of a consistent hierarchical netlist but all decisions have to be made by the designer. A more sophisticated approach would be extending the interactive tool by analysis and proposal functions.

The development of the `PLAYOUT REPARTITIONER` followed the latter idea. In order to gain experiences, we first implemented an interactive repartitioning toolbox without any sophisticated functionality. A graphical user interface supports the designer in performing basic repartitioning steps. For example, we can generate a new cell at any level of the hierarchy (i.e. a new node in the hierarchy tree), replacing a set of selected cells. These cells become subcells of the new cell and thus move down in the hierarchy. Delete is the reverse operation. We can also move cells from one location in the tree or graph to another. The distinction between tree and graph operations is the difference between changing only one instance and the type of a cell, respectively. In the latter case a change affects all instances of a cell (type). From these basic functions all possible changes of the tree or graph can be constructed. All functions are controlled by menus.

This basic repartitioning approach was good for first experiments only. The results were often better than automatic partitioning because we could keep the regularity and other objectives. However, it was not possible to do large changes and to consider timing problems without having analysis tools. We extended the `PLAYOUT REPARTITIONER` by such analysis functions but also by tools implementing simple strategies like “flattening of all blocks with less than 500 standard cells” [HNZ93]. Various (n-way) partitioning tools considering different objective functions complete the tool set. They are only used to suggest changes but no change will be done without designer interaction.

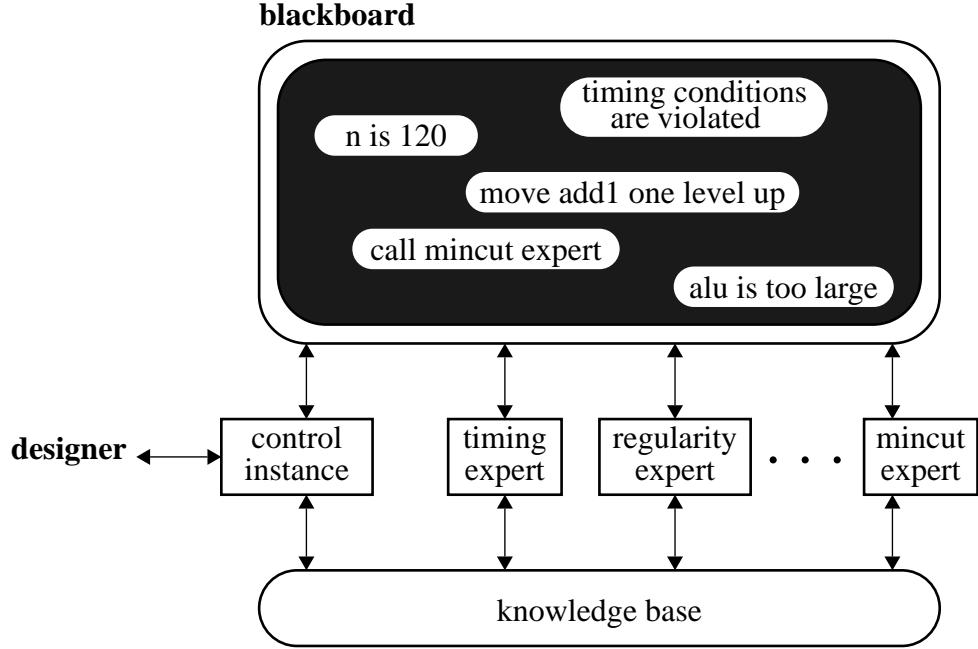

The current architecture of our `REPARTITIONER` has similarities with an expert system approach. The analysis and the suggestion tools can be regarded as experts which provide their results via the graphical, interactive interface to designer for decision making. This scenario is very similar to the AI rule-based blackboard architecture [HaR85] which is an interesting approach for our problem. The kernel of the `REPARTITIONER` corresponds to the blackboard. Additional “experts” can easily be added. The challenge of our research will be replacing the designer step by step with more automatic control instances. Nevertheless, we believe that it will not be possible to fully replace the designer within the near future. Figure 4 shows a simplified view of the blackboard approach.

## 4.2 Area Estimation

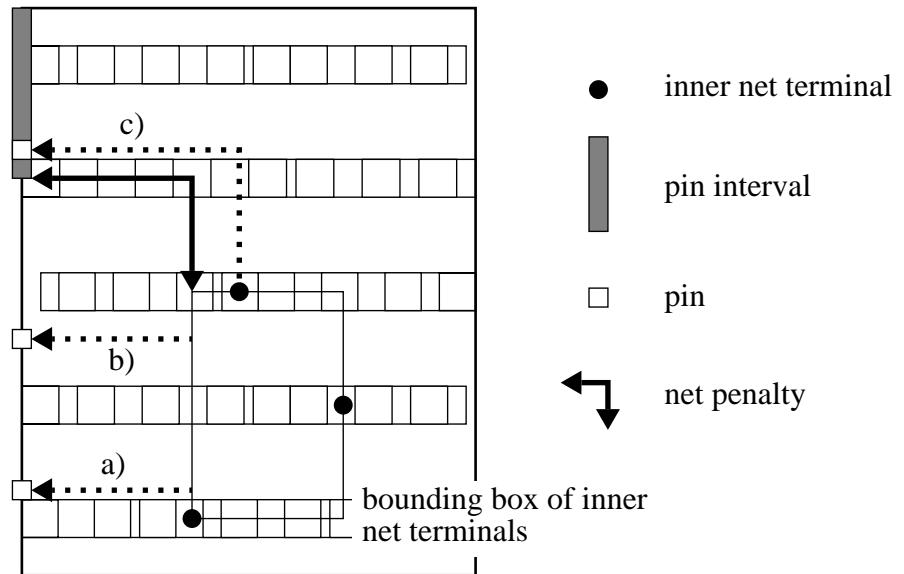

The most important part of top-down VLSI design is (top-down) chip planning. As described above, this step is divided into a bottom-up area estimation and a following top-down planning phase. Figure 5 shows the floorplan section at one hierarchy level. The left part of this figure illustrates the area estimation. Beginning at the level of the leaf cells we compute shape functions for the cells at the higher hierarchy levels. The input for an estimation step are the shape functions of the subcells and the netlist of the CUD. The output curve will be input to the area estimation at the next higher level.

Figure 4 Simplified view of a blackboard architecture for repartitioning

The shape functions are one of the most important inputs for chip planning. The planner uses the curves of the subcells and the netlist of the current cell for computing a floorplan as small as possible. For top-down chip planning, we have a further input. This is a frame with fixed dimensions and pin intervals at the border. It is a result of the preceding planning step at the next higher hierarchy level and it is based on the shape function of the current cell. The resulting floorplan should match this frame.

The output of a planning step is the floorplan that will be used by the cell assembly and the frames of the subcells which are input at the next lower hierarchy level. However, the quality of chip planning depends to a large extent on the quality of area prediction which is modeled by shape functions. In order to understand the area estimation we take a short digression into our geometric model.

Figure 5 Interaction between area estimation and chip planning

#### 4.2.1 Shape Functions

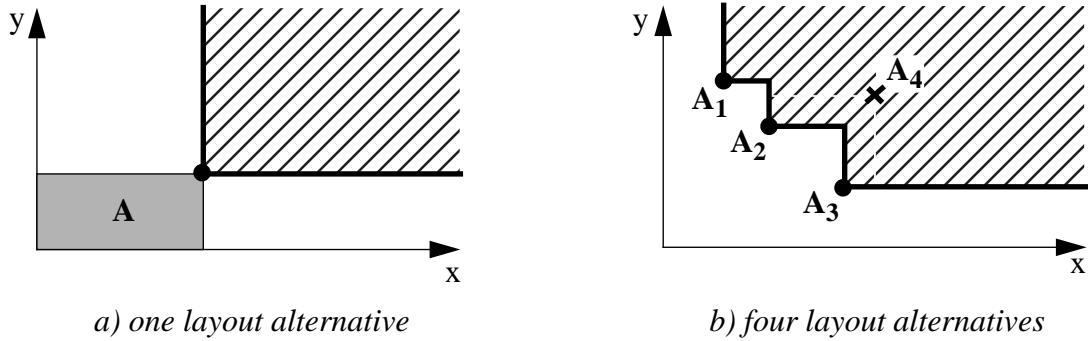

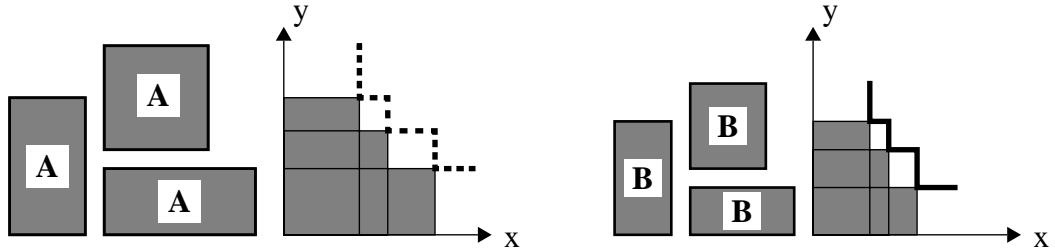

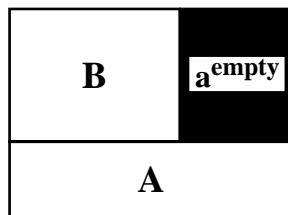

Our goal is the estimation of shape functions of rectangular layouts. Shape functions form the border between feasible and infeasible shapes. Figure 6a shows the shape function of a fixed macro cell  $A$  for which only one layout alternative exists. The black dot (corner) defines the  $x$  and  $y$  dimensions of the rectangular cell  $A$ . All other points on the curve and in the hatched area are made feasible by adding empty space to  $A$  on any of the four sides or within  $A$ . It can be used for wiring.

Figure 6    Shape function of a macro cell

IF  $A$  has different shapes (for example  $A_1, \dots, A_4$ ) by controlling the layout of  $A$  with different parameters, then a shape function as in Figure 6b evolves. Per definition as a lower area bound, the shape function is monotonic and  $A_4$  could be constructed by adding empty area to  $A_2$  or  $A_3$ . The shape function in Figure 6b is therefore fully defined by the corner coordinates  $A_1, A_2, A_3$ .

$A_4$  may have properties that neither  $A_2$  or  $A_3$  have. For example,  $A_4$  may have all pins on one side, whereas  $A_2$  and  $A_3$  have pins on all four sides. Thus, in a specific floorplan,  $A_4$  may, despite larger area, produce a smaller floorplan or a shorter critical delay path. Therefore, we do not always enforce monotony.

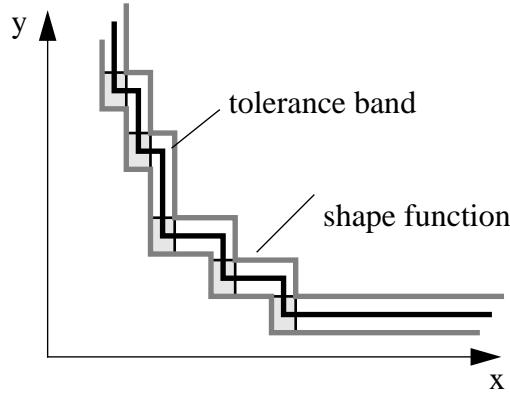

For flexible cells, only estimated shape functions can exist, if the layout style offers design decisions that influence the layout area. Thus each corner point has tolerances in  $x$  and  $y$  and the shape function has a tolerance band around the average curve as shown in Figure 7. In the extreme the shape function can be a continuous curve, but due to tolerances and design style restrictions it can always be approximated by a suitable number of corners. Module generators can be either modeled by macro shape functions if they generate fully predictable layouts or by flexible cell shape functions otherwise.

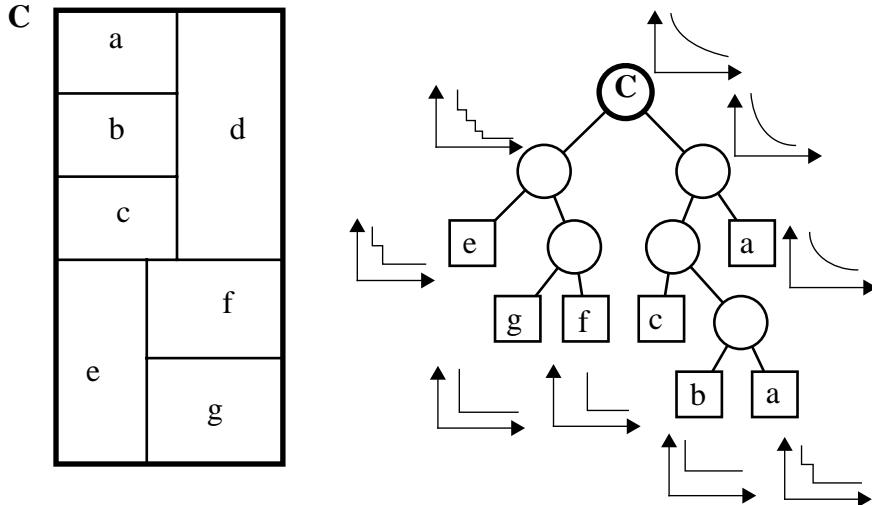

Our basic geometry is slicing. Slicing is the dominant approach in floorplanning because of features which simplify placement and routing. It is not obvious that more complex structures have major advantages. A possible extension to slicing is the deviation of the slicing lines from straight lines.

Slicing dissects the rectangle of a CUD into non overlapping rectangles representing the subcells. The walls between the subcells are the slicing or cut lines. Slicing geometries can be

Figure 7 Shape function of a flexible cell

represented by slicing trees. If shape functions for the leaves of a tree are known and the orientations of all slices in the tree are determined, the shape functions can be easily added up the tree and thus for the root node which represents the CUD [Ott83]. Figure 8 shows this correspondence.

If the orientations of the slices are not known, optimal orientations can be determined by adding monotonic shape functions horizontally and vertically and selecting the corners with minimal area of both results (see below).

The resulting shape function estimates the total area only if no additional wiring space is required. We extended the model by trying to estimate this space [Zim88]. This led to a *five color model*.

Figure 8 Slicing structure and tree

#### 4.2.2 The Five Color Model

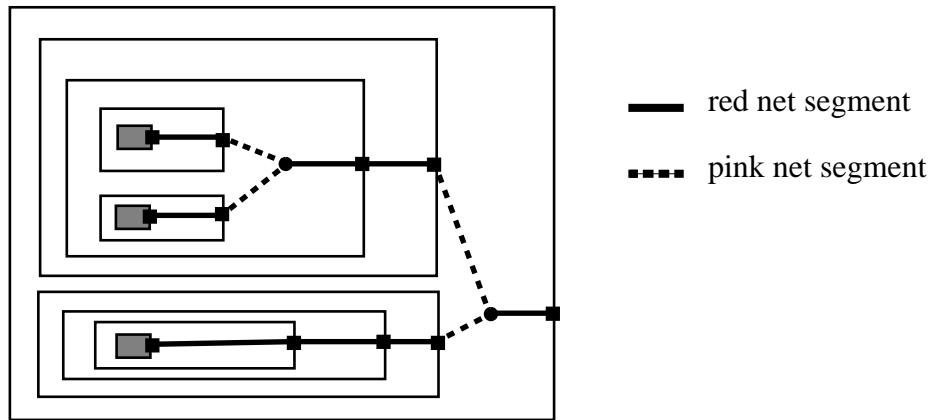

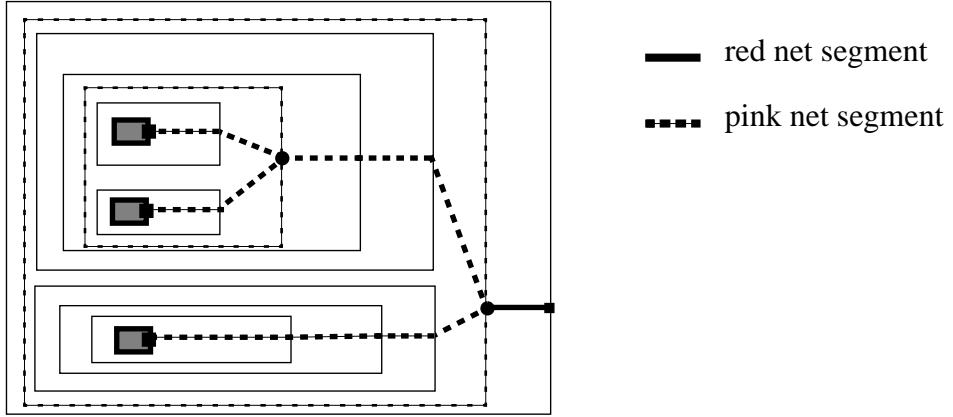

Let us look at any one level of a multi-level hierarchy and let us assume that we seek the shape function of the CUD. The CUD consists of  $n$  subcells  $sub_j, j = 1 \dots n$ . Each cell has pins at its perimeter. Nets are globally defined for all hierarchy levels. A net can therefore exist at many levels. For the purpose of estimation we divide nets into segments that are fully con-

tained in one level only.

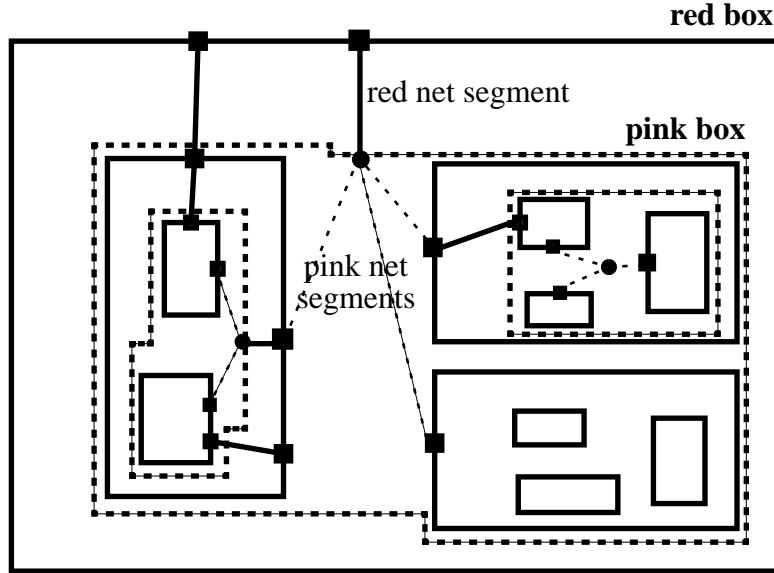

Such a net segment can be further divided into pink and red parts (Figure 9). The pink part of the net connects only the pins of the subcells  $sub_j$  but not the pins of the CUD (dotted lines). Pink segments are internal connections of a cell and exist if more than one internal pin exists. Red net segments connect pink segments (or the only internal pin of a net) to an external CUD pin (solid lines).

*Figure 9* *Pink and red net segments.*

*The figure shows net segments on two hierarchy levels.*

With this notion of net colors we define wiring area  $w^{pink}$  and  $w^{red}$  for the CUD.  $w^{pink}$  is the sum of all areas occupied by internal wiring and  $w^{red}$  is the area necessary for connecting the internal wiring with the CUD border. Accordingly we define enclosing rectangles for both colors, called the pink and the red box, resp. (Figure 9). The areas of both boxes are denoted  $a^{pink}$  and  $a^{red}$ , resp. In addition, we define a blue box with area  $a^{blue}$  for the case that all nets of the current level are disregarded.  $a^{blue}$  is the sum of all subcell areas. Note, that the blue and the pink boxes are fictive boundaries because neither all subcells nor the pink net segments are located at a particular part of the chip die without contact to red net segments. Nevertheless, we need the sizes of these fictive boxes for area estimation.

Besides these three colors pink, red, and blue, we use a fourth color black which denotes the empty space (wasted area). This is the area which is neither occupied by the subcell nor by wiring. Since the empty space is spread over the whole CUD, no concrete black box can be extracted. We only use the total amount of empty area for the estimation. This value is denoted by  $a^{empty}$  or  $a^{black}$ .

In our estimation model, the different colored areas are computed as follows:

- The area of the (fictive) blue box is the sum of all subcells<sup>2</sup>:

$$a^{blue} = \sum_j a_{sub_j}^{red}. \quad (1)$$

- The pink area includes the blue box (i.e. the subcell area), the area occupied by the pink wiring segments, and the empty space:

$$a^{pink} = a^{blue} + w^{pink} + a^{black}. \quad (2)$$

- The red area contains the pink area and the area of the red wiring segments connecting the internal wiring with the CUD boundary:

$$a^{red} = a^{pink} + w^{red}. \quad (3)$$

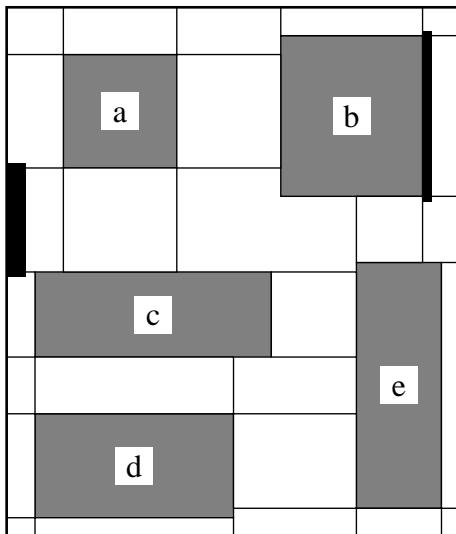

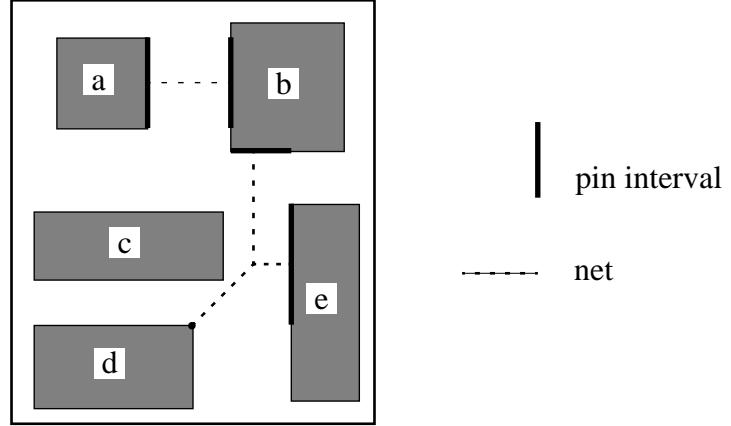

For performing floorplanning, these four colors are not enough. We further have to consider the wiring external to the CUD which we denote by the color green. Figure 10 depicts this aspect. Figure 10a shows a floorplan with five subcells *a*, *b*, *c*, *d*, and *e* (gray blocks). We assume the wiring to be located in channels between these blocks. The white rectangles describe channels and the white polygons connecting the channels describe switchboxes. The black boxes model the empty space.

*a) red subcells and wiring channels*

*b) assigning wiring area to the subcells*

*Figure 10 Floorplan with five subcells*

For computing a correct geometry of the floorplan we have to assign fitting shapes to the subcells. This is done by adding up the shape functions of the subcells and then distributing the CUD area to the subcells with respect to this shape functions (see Section 4.3). For that purpose, the subcell shape functions must include all wiring area. We assign the channel and

---

2. Corresponding to our color model described so far, the boundaries of the subcells are equal to their red boxes. They include all sub-sub-cells (sub-2-cells) as well as the whole internal (pink and red) wiring area and empty space. With that, layout frames are red, too.

switchbox areas to the adjacent subcells which results in a slicing topology as depicted by Figure 10b. The five rectangles now include the (red) subcell areas and the inter-cell wiring  $w^{green}$ . We assign the color green to these rectangles:

$$a^{green} = a^{red} + w^{green} \quad (4)$$

We need this notion during floorplanning of the CUD because  $w^{pink}$  and  $w^{red}$  are useless parameters for the placement of the subcells:

$$w_{CUD}^{pink} + w_{CUD}^{red} = \sum_j w_{sub_j}^{green}. \quad (5)$$

#### 4.2.3 Shape Function Arithmetic

The input to the shape function computation are the shape functions of the subcells and the netlist of the CUD. Output should be the shape function of the CUD. Since we restrict to slicing structures, we first compute a binary slicing tree by a partitioning step (see Figure 8). We compute the shape functions of the inner nodes of this tree bottom-up until we get the curve of the root node (CUD). The task of each iteration step is to combine the shape functions of two sibling nodes in the tree to get the shape function of their common father node as result.

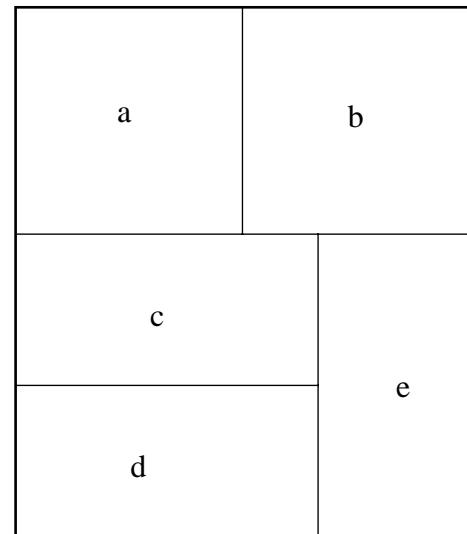

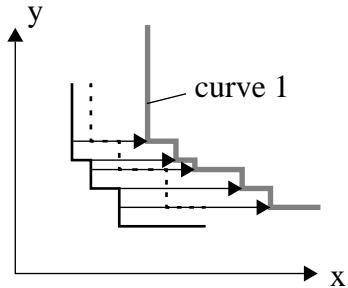

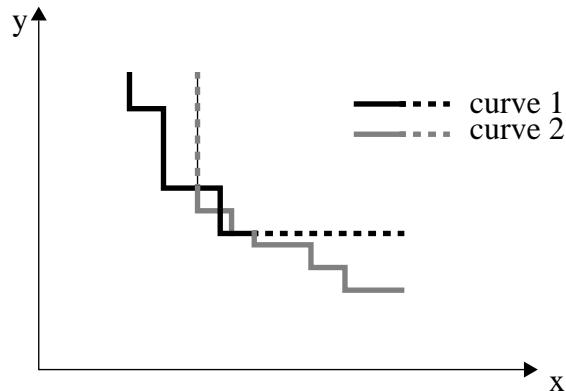

##### a) Adding two shape functions

Let us assume that we have two sibling nodes  $A$  and  $B$  in the slicing tree which have a common father node. For the example we further assume that both nodes are leaf nodes. However, the procedure described below works identically for all other nodes in the tree. For both nodes we have three different layout alternatives. Figure 11a shows these alternatives and the corresponding shape functions.

We now can place cell  $A$  beside cell  $B$  or we can place  $A$  above or below  $B$ . Depending on the orientation of the slicing line, we get two different shape function for the common father node. The vertical cut, this means cell  $A$  is placed beside cell  $B$ , results in the curve of Figure 11b and a horizontal cut results in the curve of Figure 11c. In all cases, the bounding box of the father node contains more or less empty space which is the result of the slicing topology.

Both curves have to be combined to get a single shape function for the father node. The resulting shape function must again describe the lower bound of all feasible shapes. So, the unification procedure takes those curve segments from *curve 1* and *curve 2* which form this lower bound (Figure 12). In our example, the result is the curve which is shown by the solid black and gray line. Each corner point gets a tag that denotes the cut orientation with minimal area consumption. We call this: *optimal orientation*.

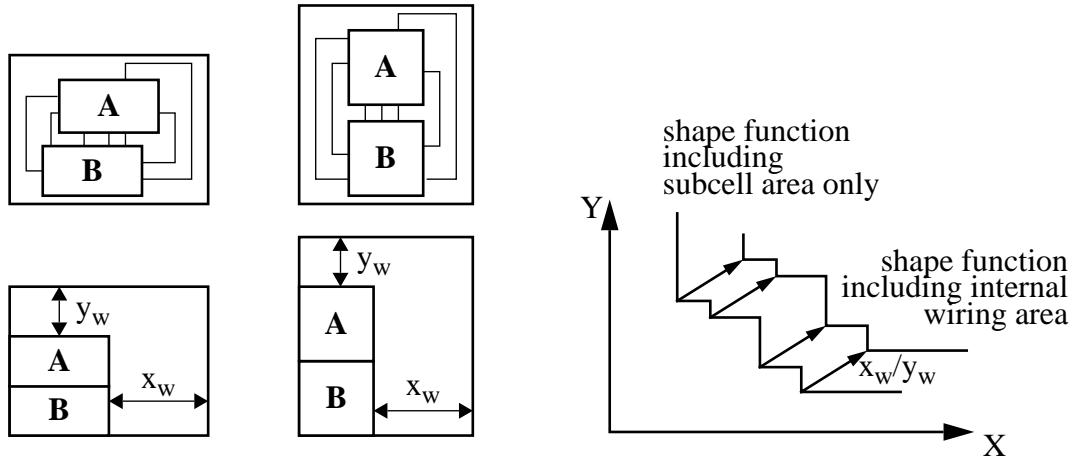

Until now, we considered only the subcell areas which resulted in a correct shape function for the common father node. On the other hand, no wiring space has been considered. This wiring space widens the cell area in horizontal and vertical directions. The combined shape function has to be shifted to the top and the right. This shifted curve would be input to the shape function computation at the next higher level.

a) layout alternatives and shape functions of two sibling cells

b) horizontal addition

c) vertical addition

Figure 11 Horizontal and vertical addition of two shape functions

Wiring area can be divided into the pink *internal wiring* and the red *external wiring*. For combining two sibling nodes, the pink net segments of the father node are segments which have connections to both sibling nodes only. They cross the corresponding slicing line. Red net segments have connections to at least one of the two child nodes and any node outside the considered subtree. They may be pink net segments of an ancestor node.

This distinction between pink (→ internal) and red (→ external) wiring is necessary because the area needed for external wiring depends very much on the positions of the pins on the cell border which are not known during the bottom-up area estimation phase. Our basic area estimation model is therefore based on pink wiring only that can be very well estimated without geometrical informations.

Figure 12 Combining two shape functions

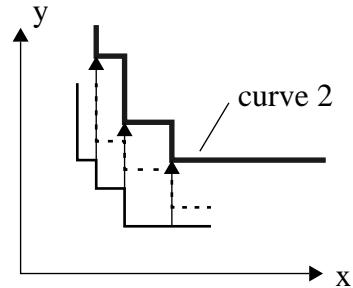

Independent of the shape of a cell, we estimate the area needed to connect its subcells, i.e. the increase of the cell area due to the pink wiring, by the following simple functions (Figure 15):

Figure 13 Wiring Area Estimation.

The shift of the shape function is independent of the shapes.

$$x_w = n_{\text{pink}} \cdot t_x \cdot \alpha_x \quad (6)$$

$$y_w = n_{\text{pink}} \cdot t_y \cdot \alpha_y \quad (7)$$

Wires between the subcells need additional space in x and y direction, called  $x_w$  and  $y_w$ . The horizontal enlargement  $x_w$  of the cells is estimated by multiplying the number of internal wires connecting the subcells ( $n_{\text{pink}}$ ) with a statistical track demand factor  $t_x$  and a technology dependent scale factor  $\alpha_x$ .  $t_x$  determines how many vertical tracks a single wire needs on the average. It models the quality of the layout tools and routers. The value is typically about 0.6 which means: one wire needs a little bit more than a half track on the average.  $\alpha_x$  is a scale factor describing the width of a single track. It depends on the design rules. The vertical enlargement  $y_w$  is estimated accordingly. In total, we have a constant shift of the shape function to the top and right (right side of Figure 15).

### b) Feedthroughs

A still open problem is the empty space (wasted area) that occurs due to the corners in the shape functions. If we set two cells on top of each other as shown in figure 14, the composite cell gets the maximum of both x dimensions and the sum of the y dimensions. The difference in x results in empty space  $a^{\text{empty}}$ .

Figure 14 Empty space

In our model, we assume that empty space increases the transparency of a cell. Transparency is modeled by vertical and horizontal feedthroughs. Standard cells, for example, have built-in feedthroughs perpendicular to the row. We measure vertical feedthroughs by the wiring space  $xf$  in the x-dimension of a cell. The empty space  $a^{empty}$  of cell B in figure 14 is modeled as wiring space  $x^e$  and thus

$$\hat{xf}_B = xf_B + x^e. \quad (8)$$

$\hat{x}$  denotes an area with empty space added. The question now is: What is the vertical transparency of the combined cell  $AB$ . We use the weighted sum of two extremes. One extreme takes the average of the sum of the transparencies of  $A$  and  $B$ , the other the minimum. This results in

$$xf_{AB} = c \cdot \frac{\hat{xf}_A + \hat{xf}_B}{2} + (1 - c) \cdot \min(\hat{xf}_A, \hat{xf}_B). \quad (9)$$

A large set of measurements with our design tools has shown that  $xf_{AB}$  is much nearer to the minimum than to the average. We set  $c \ll 1$ . The horizontal transparency in this example is easily computed, because no empty space has to be considered:

$$yfc_{AB} = yfc_A + yfc_B. \quad (10)$$

The case of cells with a vertical slicing line is handled accordingly. In the calculation of wiring space the feedthrough dimensions are subtracted from the needed wiring space for nets. Any remaining feedthrough space is propagated up in the slicing tree.

#### 4.2.4 Hierarchical Models

Until now, we considered the area estimation on one hierarchy level. We construct a binary slicing tree and add the shape functions of the subcells up in the tree until we get the shape function of the CUD. Wiring area, empty space, and transparencies are considered as described in Equation (6) to (10).

The hierarchical bottom-up area estimation over several hierarchy levels can be done in the same manner. We (virtually) combine the slicing trees of all hierarchy levels into one large slicing tree (Figure 15). In this big (virtual) tree, we pairwise add up the shape functions as described above.

The open question for this approach concerns the type of the gray nodes in Figure 15, i.e. the type of the elements of our cell hierarchy. For the shape function arithmetic we only considered internal wiring and with that pink area only. On the other hand, we previously mentioned that the subcells in the cell hierarchy are red or eventually green during floorplanning (when we add the wiring channels to the subcell areas). With that, there may be three different hierarchical models depending on the color of the cell: a *hierarchical red model*, a *hierarchical pink model*, and a *hierarchical green model*. They will now be shortly discussed.

##### a) Hierarchical Red Model

Macro cells, i.e. layout boundaries, as well as the subcells which are used for floorplanning are red. They include all wiring to the cell boundary. It may be obvious that all elements of the

Figure 15 *Cell hierarchy tree and corresponding slicing tree.*

During area estimation, we expand the  $n$ -ary hierarchy tree to a binary slicing tree. The shape functions of the gray nodes in the slicing tree are the shape functions of the corresponding nodes hierarchy tree.

cell hierarchy are modeled as red boxes. They can be defined recursively using equations (1), (2), and (3):

$$a^{red} = \sum_j a_{sub_j}^{red} + w^{pink} + w^{red} + a^{black} \quad (11)$$

This definition of a hierarchical model has two disadvantages. The first one is the fact that a net may pass through several levels of the hierarchy without connecting more than one internal pin, that means without pink segments (Figure 16). No good model is known for the estimation of a chain of red segments over several levels. The second disadvantage is that the area necessary for red wiring depends very much on the positions of the pins on the cell border which are not known during the bottom-up area estimation phase.

Figure 16 *Chain of red net segments*

### b) Hierarchical Pink Model

Because of the disadvantages of the recursive red model, we use a recursive pink model during area estimation. In order to get rid of the red net segments, we add all red segments to the next pink segment on a higher level. Figure 17 explains this notion. The pink net segments and

the pink boxes are shown by dotted lines. The extension of the pink segment yields an increase of the pink wiring area per net which is described by  $\tilde{w}^{pink}$ .

Figure 17 *Pink net model.*

This example has three pink net segments.

The pink recursion can then be described by the area equation

$$a^{pink} = \sum \tilde{a}_{sub_j}^{pink} + \tilde{w}^{pink} + a^{black}. \quad (12)$$

Our pink model has proven its quality for many standard cell and flexible cell examples. Some results are shown in Section 6. Our `SHAPE FUNCTION GENERATOR` therefore strictly uses the pink model for the complete slicing and hierarchy trees. In order to use a shape function for floorplanning at any hierarchy level, the additional red wiring space has to be added at that level:

$$a^{red} = a^{pink} + w^{red}. \quad (13)$$

Here,  $w^{red}$  is the red wiring area at the level of floorplanning only. We call this additional space the *red shift*. It will be discussed in the following Section.

### c) Hierarchical Green Model

We mentioned above that for computing a correct geometry during floorplanning green boxes are needed. The green area  $a^{green}$  includes all subcell areas  $a^{blue}$  and the whole wiring area  $w^{pink} + w^{red} + a^{empty}$  of the CUD. With that, it is easy to see that:

$$a^{green} = \sum_j a_{sub_j}^{green} \quad (14)$$

This is the most simple recursive equation. Nevertheless, the hierarchical green model is not applied in practice because floorplanning will always be done at one hierarchy level only.

### 4.2.5 Red Shift

The reduction to internal wiring results in a uniform, correct hierarchical area estimation model. Only for the top-level cell and during top-down chip planning we need an estimation of the wiring area to the cell/chip border. In this Section, we will show that the layout area of a

given cell often depends very much on the position of the pins. During top-down chip planning, we use a more precise model for estimating the subcell areas which consist of internal wiring and external wiring to the subcell border.

We are now interested in knowing the influence of pin positions on the overall area. At least the chip planner must know this effect because the planner must reserve room for the subcells in a floorplan including all wiring area inside the subcells.

In our first area estimation approach, we estimated the external wiring area of cells with random pin positions [Zim88]. This led to a shift of the shape function to the top and right which was the same for all points on the curve. However, a large set of measurements has shown that this assumption is not true. The measurements showed that the influence of restricted pin positions is too large to use random pin distributions for the estimation.

In our new approach, we prefer a two-phase estimation concept. During bottom-up estimation before chip planning (phase I) we estimate the cell area including subcells and internal wiring only. External wiring will not be considered (see above). This area is very close to the smallest possible layouts of a cell for all aspect ratios. The additional areas which are needed for external wiring will later be estimated by the chip planner (phase II).

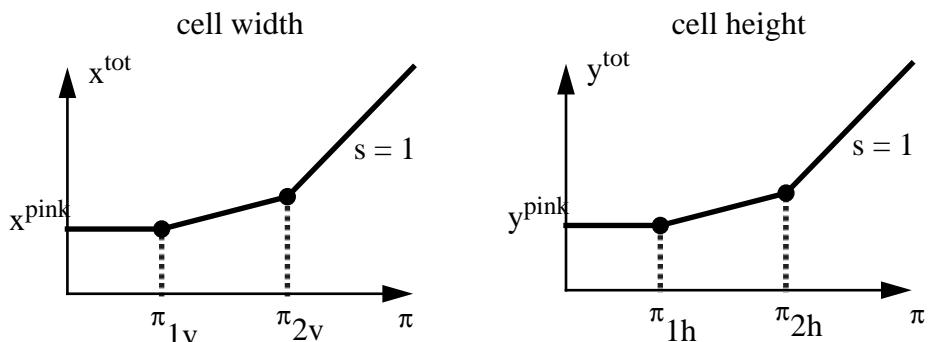

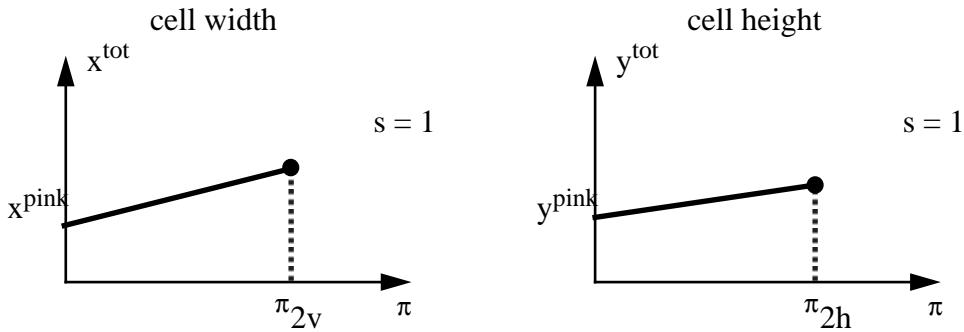

External wiring enlarges cells in x and y dimensions. We basically estimate the additional area with a function that is explained below and illustrated by the curves in Figure 18. The curves describe the total cell side length  $x^{tot}/y^{tot}$  with respect to the number of pins (or external nets) which we describe by the letter  $\pi$ .  $\pi_t, \pi_b$  is the number of pins at the top and bottom sides and  $\pi_l, \pi_r$  are the pins at the left and right sides, resp.

Figure 18 Cell dimensions with respect to the number of entering nets

In general, we have two similar curves for the horizontal and vertical sides of a cell. These curves consist of three segments which are separated by two points  $\pi_{1v/h}$  and  $\pi_{2v/h}$ . The first segment is a horizontal line. Its value ( $x^{pink}/y^{pink}$ ) is the width/height of the cell including internal wiring only.  $\pi_{1v/h}$  represent the number of built-in feedthroughs which are not used for internal wiring  $w^{pink}$ . They can now be used for external wiring  $w^{red}$  without increasing the cell dimensions. As long as all built-in feedthroughs are not occupied the whole side length ( $x^{tot}$  and  $y^{tot}$ , resp.) is equal to the length of the side while considering internal wiring only ( $x^{tot} = x^{pink}$  and  $y^{tot} = y^{pink}$ , resp.). For horizontal increase of the cell we consider vertical built-in feedthroughs  $xf$  only. The horizontal feedthroughs  $yf$  are used for computing the cell height.

The second curve segment represents an estimation method that is similar to estimating internal wiring. If we have more incoming nets than we can compensate by feedthroughs, we multiply each additional net by a special track demand factor  $t^{red}$  for external nets and, again, by the scale factor  $\alpha$  representing the design rules.

For both segments together we estimate the total cell boundaries including external wiring as follows:

If  $\pi_t \leq \pi_{2v}$  and  $\pi_b \leq \pi_{2v}$  then:

$$x^{tot} = x^{pink} + \left( \max\left[ (\pi_t + \pi_b) \cdot t_{xv}^{red} + (\pi_l + \pi_r) \cdot t_{xh}^{red} - xf, 0 \right] \cdot \alpha_x \right)$$

If  $\pi_l \leq \pi_{2h}$  and  $\pi_r \leq \pi_{2h}$  then:

$$y^{tot} = y^{pink} + \left( \max\left[ (\pi_t + \pi_b) \cdot t_{yv}^{red} + (\pi_l + \pi_r) \cdot t_{yh}^{red} - yf, 0 \right] \cdot \alpha_y \right)$$

Let us look at the first formula in more detail. It computes the total cell width  $x^{tot}$ . As long as the number of vertical incoming nets  $\pi_{t/b}$  is smaller than the second threshold value  $\pi_{2v}$  we add the pins at the top and bottom sides and multiply the sum with a horizontal track demand factor for vertical incoming nets ( $(\pi_t + \pi_b) \cdot t_{xv}^{red}$ ). We similarly add the pins at the left and right sides and multiply the sum with a horizontal track demand factor for horizontal incoming nets ( $(\pi_l + \pi_r) \cdot t_{xh}^{red}$ )<sup>3</sup>. The sum of both terms is the number of necessary vertical tracks for external wiring which increases the cell width.

From that number we subtract the number of vertical feedthroughs  $xf$ . As long as these feedthroughs are not occupied, we can compensate these with external wiring. The cell width will not increase ( $x^{tot} = x^{int}$ ). Since the number of built-in feedthroughs may be larger than the requirement for external wiring, we must take care that the subtraction does not become negative ( $\rightarrow \max$ -function).

Finally, we multiply the remaining track number with the scale factor  $\alpha_x$  to get the additional width of the cell for the entering nets. The second formula computes the cell height  $y^{tot}$ . It is similar to the first function. We just use different track demand factors and the vertical scale factor  $\alpha_y$  as well as the horizontal feedthroughs  $yf$  and the vertical side length  $y^{int}$ .

The third curve segment is needed for the case that the capacity of a side  $\pi_2$  is smaller than the associated number of entering nets. The capacity of a side depends on the design style and must be determined experimentally (see below). If the number of pins on a side exceeds the capacity, each additional entering wire needs a whole track. The slope of the curve is therefore one. In the case that the number of entering nets at two opposite sides both exceed the capacity of the side ( $\pi_2$ ) some entering nets can pairwise share a track. In this case we assume that the saturation point  $\pi_2$  is not reached. We first compute the difference between the numbers of pins

3. Nets entering from the left and right sides also increase the cell width but less than vertically entering nets. At floorplan level we set  $t_{xh}^{red} \approx 0, 2$  and  $t_{xv}^{red} \approx 0, 5$ .

at two opposite sides. Only for this difference we add whole tracks.

### Design styles

As mentioned above, the track demand factors, the number of built-in feedthroughs, and the capacity depend on the design style. They also depend on the number of metal layers. Until now, we examined two different cell types and design styles. The first class are general cells for which we do chip planning. The second class are standard cell blocks.

If we have *general cells* and we allow over-the-cell routing, the functions for external wiring are the same as described above (figure 18). Before we have to extend the cell dimensions we fill-up the subcell feedthroughs which are not used by internal wiring. With two metal layers for routing, typically no built-in feedthroughs are left. The problem class is then the same as for chip planning without over-the-cell wiring. We can assume:

$$\pi_{1h} = \pi_{1v} = 0.$$

*Figure 19 External wiring area for general cells without built-in feedthroughs

The saturation point  $\pi_2$  will never be reached for practical applications.*

All entering nets need additional wiring space. For our test designs the entering net number  $\pi$  belongs to the second curve segment in all cases. The pin number will be multiplied with the track demand factors shown above.

Determining the saturation point  $\pi_2$  is not so easy for general cells. We can only find  $\pi_2$  if the general cell contains rigid macro subcells and the aspect ratio of the general cell is far away from one. In practice we never reached  $\pi_2$ . This has two reasons. First, pins occupy only a small amount of the frame which is below the capacity. The second, much more important reason results from the design style. As we mentioned above, estimating external wiring is important for top-down chip planning. In this case, the subcells of the considered general cell are not yet designed, their shapes are still flexible. They can easily be adjusted to the channel widths. In practice, we have so much flexibility for designing general cells that using the second curve segment, i.e. multiplying the number of entering nets with a track demand factor, is sufficient:

$$\pi_{2h}, \pi_{2v} \rightarrow \infty.$$

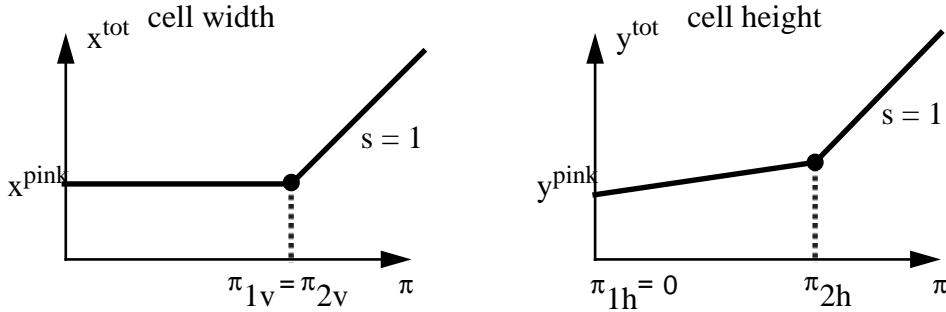

The second design style we examined experimentally are *standard cell block* layouts. We assume horizontal rows for this paper. Here it is reasonable to have no pins to the side of cell rows. An upper bound of the capacity of the vertical sides is therefore equal to  $y^{pink}$  minus the accumulated height of the rows. This is the sum of all channel heights.

Figure 20 External wiring area for standard cell blocks

Experiments have shown that this value is too high for the threshold point  $\pi_2$ . We achieved good results by setting

$$\pi_{2h} = 0.2 \cdot (y^{pink} / \alpha_y).$$

Since standard cells do not have horizontal built-in feedthroughs, the function  $y^{pink}$  has the same shape as for general cells without built-in feedthroughs (figure 20). For the cell height we have

$$\pi_{1h} = 0.$$

For the cell width the conditions are different. Here we experimentally found the following: If we have a good standard cell placement tool, most of the standard cells with connections to the top and bottom sides of the block are not placed in the center of the block but near the top or bottom row. The occurrence of these cells decreases with their distance from the block border. On the other hand, built-in feedthroughs are used for internal wiring mainly in the center of the block.

The feedthroughs in the top and bottom rows are not needed for internal wiring. In the center where we have only few unused feedthrough we do not have many cells connected to external nets. In most cases, nets can enter from top and bottom without enlarging the block. Unused feedthroughs compensate the track requirement for external wiring.

Our experiments have shown that the number of feedthroughs at the outermost rows is an indication for the capacities of the top and bottom sides ( $\pi_{2v}$ ). In the case that all these feedthroughs are used, each additional entering net needs a further feedthrough and therefore a whole track. On the other hand, as long as we still have unused feedthroughs, the width of the standard cell block does not increase due to external wiring. This means that we do not have the second curve segment for  $x^{tot}$  of standard cell blocks.  $\pi_{1v}$  is equal to  $\pi_{2v}$  in this case (Figure 20). For our standard cell placement tool and the currently used cell library we have

$$\pi_{1v} = \pi_{2v} = 0.5 \cdot (x^{int} / \alpha_x).$$

In our test designs, i.e. in practical applications, we very seldom reached this capacity.

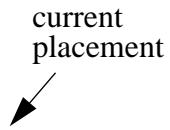

### 4.3 Chip Planning

The purpose of chip planning is the placement of (rectangular) blocks, the determination of their shape, and global wiring. Global wiring determines channel or over-the-cell routing requirements, assigns nets to channels and determines pin-cost functions. The goals are minimal area, a solution to net length limits, and an estimation tolerance that allows chip assembly

without iterations through chip planning and without loss in layout quality.

The major phases of the **PLAYOUT CHIP PLANNER** are *placement*, *sizing* and *global routing*. Especially for placement several algorithms can be selected. Placement can be improved by manual interaction. The **CHIP PLANNER** therefore has a menu-controlled user interface. The floorplan computation is supported by a number of important analysis tools. Besides the interactive control, the **CHIP PLANNER** can be controlled by a control command file. This is important for the design control by the design manager of the **PLAYOUT CAD** framework.

### 4.3.1 Placement

Placement should ideally not be separated from global routing. But it has been shown that already subtasks of placement are np-complete (see [Len90]). Therefore we even separate placement into several phases.

The restriction to slicing structures and its representation as slicing tree suggest as a first step the generation of the tree. The slicing geometry (topography) is fully described by the tree if it is oriented and ordered and if the leaf nodes are sized. In detail this means:

- Orientation: Every intermediate node is labeled v (vertical cut line) or h (horizontal cut line).

- Ordering: The ordering of siblings in the tree from left to right means ordering in the floorplan from left to right and bottom to top, respectively.

- Sizing: Dimensions (x, y) are chosen for all leaf cells. This is equivalent to choosing coordinates on the green shape function.

The topology is described by the oriented and ordered slicing tree. Without orientation and ordering we call it the unoriented tree. In **PLAYOUT**, the unoriented tree can be generated by clustering or partitioning. The **CHIP PLANNER** has a clustering algorithm as reported in [RRZ84] and a bipartitioning tool that implements the mincut algorithm [FiM82]. Cell area is used for balancing the tree. A disadvantage of these simple methods is that the position of the CUD pins (→ pin cost function) is not considered. To prevent this disadvantage, **PLAYOUT** further uses quadri and tri partitioning at the CUD level. For all possible topologies of four or three slices and for known CUD pin cost functions, the partitioning with pin propagation of the set of subcells is sought. Below this level bipartitioning takes place (considering pin location as much as it is possible without orientation). This generates a tree with an oriented ordered subtree at the root.

The topology is generated by either a combined orientation and ordering algorithm or by optimal orientation (Section 4.2.3, page 17) and a separate ordering algorithm. Both algorithms proceed in the same manner. In a breadth first traversal, subtrees with k levels are selected and in these subtrees all permutations are tested. Simple tests consider half-perimeter lengths of net bounding boxes. Better results have been achieved by calculating the shape functions for the roots of the subtrees for all permutations and then select the permutation with the area minimum. Runtime and quality increase with increasing k.

Placement is finished by sizing. Sizing calculates the shape function of the CUD for a given

orientation and selects the CUD dimension closest to the given CUD frame. This sizing is simply the application of vertical or horizontal shape function adds in the topology. Note that the CHIP PLANNER has to add green subcell shape functions while the SHAPE FUNCTION GENERATOR calculates pink functions. The CHIP PLANNER also adds wiring space to correct for intersibling wiring and which results in pink CUD shape function. This will be corrected by a red and green increase for nets external to the CUD. This increase is distributed to all green subcells.

The resulting topography includes an area estimate for global wiring without exact knowledge of the wiring channel distribution. This will be refined after global wiring.

#### 4.3.2 Global Wiring

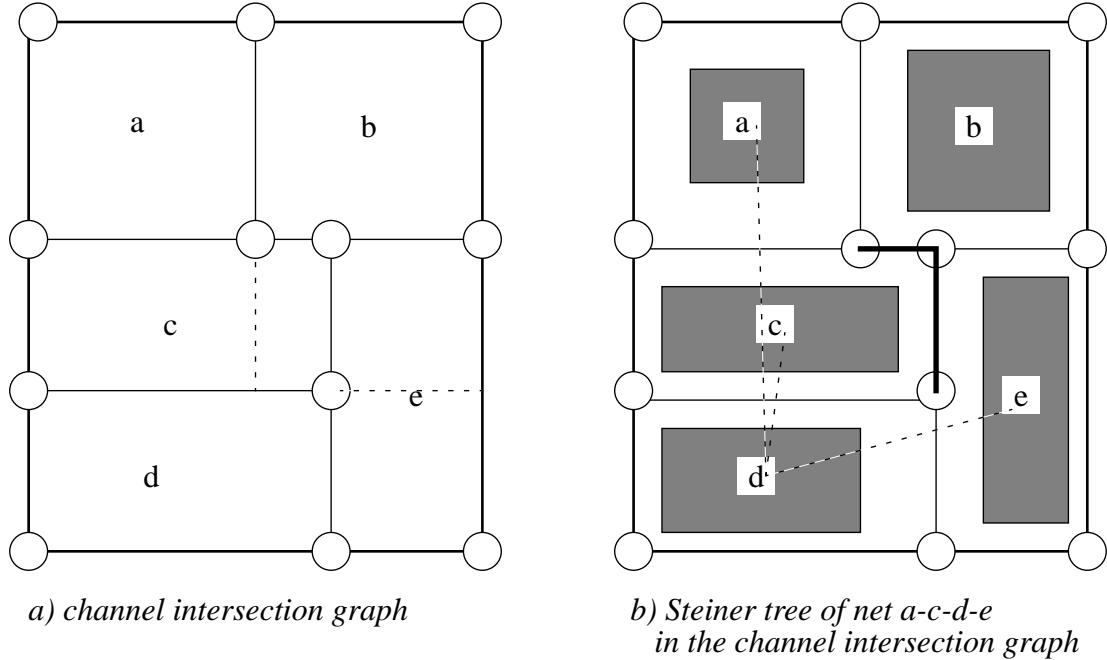

Global wiring is performed on a channel intersection graph which is an abstraction of the channels to segments of the slicing lines. The channel widths are the capacities of the edges of the channel intersection graph. The nodes are the intersections of slicing lines. Figure 10 shows an example. For the purpose of over-the-cell routing, the channel intersection graph is extended by pseudo-channels. This can either be done by extending slicing lines across the CUD or by introducing edges across the sub-cells (dotted lines). Built-in feedthroughs are modeled by pseudo-channel capacities.

Figure 21 channel intersection graph to the floorplan from figure 10

Global routing does not find the best routing for a given channel capacity, but determines the channel capacities for the best routing path of each net. Only in the case of subcells with fixed over-the-cell routing capacities (e.g. macro cells), the router is constrained by channel capacities.

Global routing demonstrates one peculiarity of planning most clearly: decisions are deferred as long as possible if the information may still grow. Therefore, if a net has to be connected to

a flexible cell, global routing terminates the net at a node of the channel intersection graph on the green outline of the cell. The pin assignment is deferred. Global routing uses a heuristic to determine a Steiner tree for each net on the channel intersection graph. At this point the green box is sufficient for routing. Exceptions are macro cells, because pin locations are fixed. The location of the red box of macro cells in the green box has to be estimated in order to find the corners adjacent to each of the pins. Global routing then proceeds as before.

Global routing results in net counts for each edge in the channel intersection graph (channel). Three types of nets have to be distinguished: A net that passes through a channel needs a full track. A net that enters a channel and ends there will need part of a track, determined by a track demand factor. A net which is local to one channel is called abutting and typically has a small track demand factor.

At first, all nets end at nodes of the graph and thus only passing nets occur. A net is abutting if it is degenerated to one node. It then has to be determined from the geometry of floorplan which edge has to provide wiring space. Determining the exact pin positions on the red boxes is deferred until the next lower level of the hierarchy is planned. Because these ending nets cannot be totally neglected, we add corresponding estimated area to the red box of the connected cell. After the numbers of tracks are determined, the width of all channels is calculated. This is followed by an optimal distribution of the channel areas to the green areas of the sub-cells.

Finally, pin intervals are determined for each pin that is not fixed. The pin interval is defined at the perimeter of the red box. If we move the pin out of this range, extra inter-subcell wiring will be necessary. This area has to be provided by the red cell. Reasons for moving pins out of the interval may be the pin capacity of the interval or the placement of the sub-subcells within the subcell of the CUD.

Figure 10 shows an example of pin intervals with four different cases. We assume two nets to be part of the floorplan of Figure 10. One net connects the cells *b-d-e*. The interval at cell *b* is the projection of the channel, at cell *e* the passing area, and at cell *d* the upper-right corner. The second net shows an abutment situation. Here, the intervals are the projection of the abutting cell sides on each other.

In conclusion, the results of global routing are:

- A more precise floorplan based on the additional knowledge of the channel widths.

- Pin-cost-function for all subcell pins.

- Assignment of nets to channels for detailed routing.

### 4.3.3 Global Wiring Iteration

Global wiring in the first iteration was based on a floorplan with estimated routing area requirements. The resulting floorplan may have different dimensions. In the general case the changes are not large enough to justify a new placement, but we can repeat global wiring for this new floorplan. This will again cause changes and may be repeated indefinitely.

These iterations can only have one goal: The improvement of the design. Currently we use

Figure 22 Pin intervals of two nets

the total CUD area as a measure of quality. Therefore we iterate as long as the area decreases. Our experience so far shows that a minimum is normally reached after one or two iterations. Also, the area gain caused by iterations is in most cases less than 5%. For global wiring iterations a wiring algorithm based on restricted channel width (from the previous iteration) may be reasonable. [Mei91] describes such an approach using flow methods.

#### 4.3.4 Manual Interaction and Analysis

During the whole design process so far, the design decisions that affect the final layout the most is the placement phase during chip planning. Several combinations of placement algorithms and cost functions can be applied to find a good solution. No combination could so far be shown to be superior to others<sup>4</sup>. Thus one of the tasks of the designers is the selection of one or more combinations and the evaluation of the results. For this purpose a range of analysis tools is provided, e.g.

- Graphical display of the floorplan is used for visual inspection, determination of problem areas, and for interactive changes to the placement.

- Graphical display of the slicing tree with orientation and ordering. This shows problems in partitioning (unbalanced tree) and is used for more complex interactive placement changes as for example moves of subtrees.

- Area statistics showing the total area of selected nodes in the slicing tree and the shares of differently colored areas. This is used to roughly compare placement alternatives.

- Net lengths and a net density distribution histograms in the CUD rectangle.

- By selecting subcell or nodes in the tree, precise geometric dimensions and other details can be interrogated.

- Original and final shape functions can be viewed for selected nodes in the tree.

---

4. We did not experiment with tools like Gordian and TimberWolfMC because our goal is the development of the overall top-down design method not individual algorithms.

Currently, interactive changes of the placement are supported. The topography is automatically adjusted after every change and immediately displayed. In the future, we also want to support limited repartitioning steps if no floorplan with sufficiently small empty space can be found.

Interaction also allows moving back and forth between the different phases of chip planning. Also, intermediate states can be preserved and restored at any time. Thus the design can be interrupted and alternatives can easily be compared with the option to return to the best intermediate state.

#### 4.4 3-Phase Chip Planning

The average tolerance of our area estimation method is about 10-15% [SuA95]. However, in the worst case the deviation can be substantially greater. In pure top-down chip planning, we have no chance to compensate these differences. The only possibility to react to deviations is to return to the shape function estimation phase and to change estimation parameters or to use realizations (layouts) of critical cells (using macros instead of flexible cells).

On the other hand, if we are not planning the top-most cell, it may be possible to compensate the deviation of the current cell shape with the deviations of the sibling cells. The area of the supercell should not change if the sum of all area estimations of the sibling cells is similar to the areas of the floorplans and layouts, respectively. Furthermore, all planned cells are slightly flexible because their subcells are still flexible. This flexibility increases the chance of a good balancing.

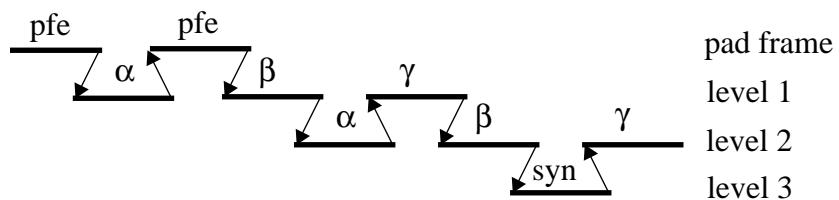

So, it is useful after computing a floorplan of the CUD to perform an *adjustment planning step* for the supercell before continuing the top-down planning process at the subcell level. The deviations at the current level can be compensated at the supercell level. Figure 23 depicts that approach. There are three planning steps which we denote by  $\alpha$ ,  $\beta$ , and  $\gamma$ . After planning the subcells at level  $i+1$  (phase  $\alpha$ ), we perform an adjustment step at level  $i$  (phase  $\gamma$ ) before con-

Figure 23 Floorplan adjustment process

tinuing the top-down planning of all subcells at level  $i+1$  (phase  $\beta$ ).

Of course, the cell at level  $i$  itself is part of an adjustment process for its supercell on level  $i-1$ . Thus, the three fundamental planning phases  $\alpha$ ,  $\beta$ , and  $\gamma$  are performed with each cell. Therefore, we call our planning method *Three-Phase Planning* [SAZ92].

The following actions are performed:

**Phase  $\alpha$  (Initial Floorplan):**

- placement

- global wiring

- wiring area estimation

- sizing (computing a correct geometry and a shape function for the CUD)

- computation of pin constraints for the CUD

The result of phase  $\alpha$  is a floorplan from which we use the topology for further planning steps and the pin constraints of the CUD for an adjustment step at the supercell level. Since the subcells are still flexible, many floorplans with different shapes but the same topology are feasible. We generate a *refined shape function* that describes all possible shapes of the same topology. This shape function is a very important input to the supercell adjustment (phase  $\gamma$ ), too. Refined shape functions are more precise than shape functions of flexible cells because they rely on a particular topology and a global routing (not only on a rough wiring area estimation).

**Phase  $\beta$  (Adjustment to new Frame):**

- global wiring (using the placement of step  $\alpha$  and the frame description from the supercell adjustment step  $\gamma$ )

- wiring area estimation

- sizing (computing the subcell shapes)

- computation of pin constraints for the flexible subcells

As we will see later, in the adjustment step  $\gamma$  of the supercell, a new frame of the CUD was computed based on its refined shape function and its pin assignments of phase  $\alpha$ . In phase  $\beta$ , we adjust the geometry of the topology from phase  $\alpha$  to this new frame.

As in the pure top-down planning strategy, we now compute the pin constraints for the subcells. The subcells can then be planned in phase  $\alpha$  (see above) which results in cells with new constraints (refined shape functions and pin constraints). These constraints are input to the CUD adjustment planning phase  $\gamma$ .

**Phase  $\gamma$  (Adjustment to more precise Subcell Data):**

- correction of the global wiring (because subcell pins can move)

- wiring area estimation

- sizing (selection of subcell shapes using the refined shape functions of the subcells)

from phase  $\alpha$ )

- computation of pin constraints for the subcells

The resulting subcell constraints (area, shape, and pin positions) of phase  $\gamma$  are used as input to phase  $\beta$  and  $\gamma$  of the subcell.

In addition, our **CHIP PLANNER** allows the designer to interactively change the floorplan in every planning phase. For example, it is sometimes necessary to change the slicing structure (and with that the topology data) without changing the adjacencies of the cells, i.e. the global topology. The global wiring may use new channels for a particular net when the topology of the slicing lines changes.

In figure 24 the three planning phases with the top-down and bottom-up data interchange are outlined. In contrast to our refined shape functions all other hierarchical top-down design sys-

Figure 24 *Chip Planner input/output during the three phases

(a floorplan is also passed from phase  $\alpha$  to  $\beta$  and from  $\beta$  to  $\gamma$ )*

tems use at most one fixed shape for an adjustment [YiW89]. They do not provide any top-down adjustment like the phase  $\beta$ .

Figure 25 shows an abstract notation of a hierarchical planning over three levels. The planings of all subcells were combined in each case. Even though there are bottom-up movements, it is obvious that the global direction of the design process is still top-down. At the top level, the pad frame is created (e.g. by our graphical **PAD FRAME EDITOR**; *pfe*) and at the lowest hierarchy level we perform the cell synthesis *syn*.

Figure 25 *Three level chip planning with adjustment*

### Stepwise Refinement

So far we assumed that all planning steps  $\alpha$  of the subcells will be performed in parallel, independently of each other. However, in several cases, balancing the floorplan in phase  $\gamma$  can be improved by generating the floorplans of the subcells step by step. On the other hand, it may be desirable to insert all critical cells first (e.g. cells which do not fit to the estimations) and to leave the remaining cells flexible which can balance the whole floorplan in a following adjustment step.

An extreme possibility for a stepwise refinement strategy is the depth-first traversal of the hierarchy tree. The advantage of this method is that we have the freedom to build critical modules (subtrees) step by step first. The disadvantage of a depth-first strategy is that we loose the whole parallelism. No planning processes can be performed concurrently.

Another possible strategy is to plan all subcells (perhaps with different topologies for each subcell) and leave the final configuration decision to the **CHIP PLANNER**. Within the adjustment phase  $\gamma$  of the CUD, the **CHIP PLANNER** chooses the most fitting floorplan alternative of each cell. Experiments have shown that there is no single best solution. The strategy with best results depends on the actual design.

### Convergence

In total, there are many possible strategies although we use only three different phases. In an extreme strategy, it is possible to descend and to ascend the hierarchy tree in a yo-yo fashion.

So, we have to show that our procedure terminates. In each bottom-up adjustment step  $\gamma$ , we always replace at least one flexible subcell by a floorplan or a layout. A floorplan will be replaced by a layout only. When all flexible subcells are replaced by a layout, the final cell assembly terminates the adjustment procedure.

While the procedure terminates for all strategies, we can see a convergence behavior when executing the stepwise refinement strategy. Here, we replace the inexact flexible cells with more exact rigid cells step by step. With each replacement, one inexact component has been removed and with that the tolerances will become smaller. The floorplan geometries converge to the final layout.

### Restrictions

In spite of all the freedoms we have, we are not permitted to build a cell and one of its subcells in parallel. Before we can make a planning step  $\gamma_k$ , we have to stop all subcell planning processes and have to collect the current results as input for the adjustment step  $\gamma_k$ . After  $\gamma_k$ , we can go on with the subcell plannings in consideration of the new constraints from  $\gamma_k$ . If we do not stop the subcell processes, we build divergent bottom-up and top-down frame descriptions.

It is the design managers task to keep track of the planning process. In [ASZ93] we describe seven rules which are implemented in our design manager. These rules guarantee the correct traversal through the circuit hierarchy. They are the basis of an automatic design management that controls a correct design flow.

Three of the seven rules correspond to the three chip planning phases.

- Rule 1 describes that phase  $\alpha$  of a CUD can be performed as soon as a frame has been computed top-down (by a planning step of the supercell) and no floorplan of the CUD has already been produced.